# Design and Simulation of 2-Bit Full Sub Tractor at 32 Nm CMOS Technologies

# M.M. Prasada Reddy

Professor, Dept of E.C.E, Nova college of Engineering & technology, Hyderabad, Telangana, 500070

Abstract- Low power and efficient area are frequently required in very large scale integration design. The Complementary Metal Oxide Semiconductor (CMOS) are used in various electronic fields viz manufacturing of digital integrated circuits, microcontrollers and microprocessors. In this paper, the proposed CMOS 2-bit full Subtractor is simulated and analyzed using Microwind 3.1at 32nm CMOS technologies. The full Subtractor is sowing good performance in terms of power dissipation and area.

*Index Terms*- CMOS, VLSI, Full Subtractor, Power consumption, CMOS technology.

### I. INTRODUCTION

The full-Subtractor is a combinational circuit which is used to perform subtraction of three bits. It has three inputs, A (minuend) and B (subtrahend) and C (subtrahend) and two outputs D (difference) and B [1].For more than four decades, downscaling of CMOS has been the fundamental strategy for improving the performance of VLSI circuits. However, there have been reports suggesting that the MOS transistor cannot shrink beyond certain limits dictated by its operating principle [2]. The speed and power dissipation are the important parameters which should be taken into consideration in digital circuits. Since number of integrated transistors become double in once in 18 months, there is a much need to fabricate low power VLSI chips. Portable consumer electronic products powered by batteries is an another factor for low power VLSI Design, since the battery technology alone cannot solve the low power problem [3]. Basically a subtractor is a digital circuit that performs subtraction of numbers or one could possibly say that it performs one of the four basic binary operations [4].

## II. SUBTRACTOR

Subtractor is a circuit which is used to do subtraction. There are two types of subtractor i.e., Half Subtractor and Full Subtractor.

# A. HALF SUBTRACTOR

The half subtractor is a combinational circuit which is used to perform the subtraction of two bits. It consists of two inputs called the minuend denoted as A and the subtrahend denoted as B and two outputs called difference denoted as D and borrow denoted as Bin [5]. The logic diagram for half subtractor is shown in Fig. 1. The truth table for the half subtractor is given in table I:

Table I. Truth Table of Half Subtractor

| Inputs |   | Outputs |                 |  |

|--------|---|---------|-----------------|--|

| A      | В | D       | B <sub>in</sub> |  |

| 0      | 0 | 0       | 0               |  |

| 1      | 0 | 1       | 0               |  |

| 0      | 1 | 1       | 1               |  |

| 1      | 1 | 0       | 0               |  |

The Boolean expression for the two output variables are as follows [5]:

$$D = A^1B + AB^1 \dots (1)$$

Fig.1 Half Subtractor using XOR, AND and NOT gate

# B. FULL SUBTRACTOR

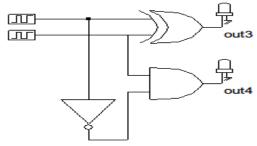

The full-subtractor is a combinational circuit which is used to perform subtraction of three bits. It has three inputs, A(minuend) and B(subtrahend) and Bin

(subtrahend) and two outputs D (difference) and Bout (borrow)[1]. Full subtractor is constructed using two half subtractor using two XOR, two AND, two NOT and one OR logic gates. The Full Subtractoris used in various VLSI application. It is widely used in microprocessors. In arithmetic logical unit they are used to perform arithmetic operations. The logic diagram for full subtractor is shown in Fig. 2. The truth table for the full subtractor is given in table II:

Table II. Truth Table of full subtractor

| Inputs |   |                 | Outputs |           |  |

|--------|---|-----------------|---------|-----------|--|

| A      | В | B <sub>in</sub> | D       | $B_{out}$ |  |

| 0      | 0 | 0               | 0       | 0         |  |

| 0      | 0 | 1               | 1       | 1         |  |

| 0      | 1 | 0               | 1       | 1         |  |

| 0      | 1 | 1               | 0       | 1         |  |

| 1      | 0 | 0               | 1       | 0         |  |

| 1      | 0 | 1               | 0       | 0         |  |

| 1      | 1 | 0               | 0       | 0         |  |

| 1      | 1 | 1               | 1       | 1         |  |

Fig.2 Full Subtractor using XOR, NOT, AND, OR logic gates

The Boolean expression for full subtractor for the two output variables are as follows [5]:

$$D=A+B+ B_{in}....(3)$$

$B_{out} = A^{1}B_{in}+A^{1}B+B B_{in}....(4)$

Dynamic dissipation and short circuit are the component of power to be considered during the input signal transition. To modify the charge content of the capacitive load, the dynamic power is dissipated and it is proportional to the switching frequency and to the load capacitance, and also depends on the area of the buffers. By the simultaneous conduction of P and N transistors during the transition of the input signal the short circuit power dissipation is produced. The ratio of input to transition times is a good indicator of short circuit power dissipation. The value of ratio should be comparable or lower than unity, and it is the objective of buffer design, the short circuit power

dissipation can be omitted. In the result just consider the dynamic component to optimize objectives. The total value of the load capacitances includes layout parasitic (diffusion and interconnect) and active loads is the minimum capacitance [6].

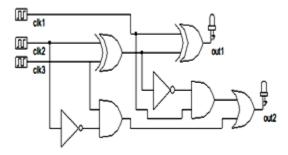

### III SIMULATION

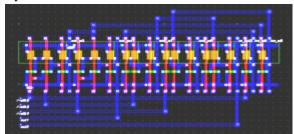

The full subtractor are compared based on the performance parameters like surface area and power dissipation. To achieve better performance, the circuits are designed using CMOS process by Microwind 3.1 in 90nm, 70nm and 50 nm technology. The proposed full subtractor circuit shown in figure 3, uses two 2-bit X-OR, two 2-bit AND, one 2-bit OR and two 1-bit NOT logic gates. All the layouts and simulation results presented here are done in Microwind3.1 which is a layout editor and simulator. On the layout presented by this tool, simulation can be done. Simulation is first performed using schematic entry and its corresponding test patterns are generated and is verified whether it is functioning properly or not. The schematic file after verification is converted to VERILOG file. Then the VERILOG file is imported using the command "compile Verilog file" using MW environment so that the schematic of the logic design will be converted into physical layout. MSK File is used to store the information of the layout design. Power dissipation, rise delay, fall delay, timing results, layout area are the performance characteristics which can be provided by this tool. There is a facility in this tool to convert layout to Caltech Intermediate Format (CIF) which provides the information for fabrication. To extract the electrical parameter there is a program EXTRACT in this tool. Metal Oxide Semiconductor Implementation Service (MOSIS) uses standard mask layout like CIF for fabrication.

Fig.3 Layout design of proposed Full Subtractor

Fig.3 Simulation output of of proposed Full Subtractor

#### IV. RESULTS

The simulation results of proposed full subtractor for 32 nm CMOS design technology are given in Table-1 Table-1: Simulation results

|                                                      | Area<br>in<br>µm² | Pow<br>er in<br>μW | Me<br>mor<br>y<br>requ<br>ired<br>in % | Nu<br>mbe<br>r<br>NM<br>OS<br>devi<br>ces | Numb<br>er of<br>PMOS<br>device<br>s | Elect<br>rical<br>node<br>s |

|------------------------------------------------------|-------------------|--------------------|----------------------------------------|-------------------------------------------|--------------------------------------|-----------------------------|

| Full Subtracto r using XOR, NOT, AND, OR logic gates | 27.9              | 0.09<br>6          | 3.3                                    | 17                                        | 17                                   | 31                          |

## V. CONCLUSION

Simulation of the proposed full Subtractor with 32 nm CMOS technologies is done. The power consumption and surface area are measured. The proposed full Subtractor is showing good performance in relation to power dissipation and area. Making little modification in full adder circuit we further reduce power dissipation and area

# REFERENCES

- [1] K. Prasad Babu, S. Ahmed Basha, H.Devanna "Design of Low Power CMOS Full Subtractor" IJISET - International Journal of Innovative Science, Engineering & Technology, Vol. 1 Issue 6, August 2014

- [2] Y.Tau, D.A.Buchanan, W.Chen, D.Frank,K.Ismail, S.Lo, G.Sai-Halasz, R.Viswanathan,

- H.Wann, S.Wind, and H.Wong, "CMOS Scaling into the Nanometer Regime," Proceeding of the IEEE, vol.85, pp. 486–504, 1997.

- [3] Yeap, G.K., 1998. "Practical Low Power Digital VLSI Design" Kluwer Academic Publishers, Norwell, MA., ISBN: 0792380096, Pages: 233.

- [4] Tanvi Sood, Rajesh Mehra "Design a Low Power Half-Subtractor Using .90µm CMOS Technology." IOSR Journal of VLSI and Signal Processing (IOSR-JVSP) Volume 2, Issue 3 (May. – Jun. 2013), PP 51-56.

- [5] Pranshu Sharma, Anjali Sharma "Design and Analysis of Power Efficient PTL Half Sub tractor Using 120nm Technology" (IJCTT) – volume 7 number 4– Jan 2014 ,Page207.

- [6] T.Thirumurugan, J.Sathish Kumar, 2012, "Energy Efficient Implementation for Arithmetic Application in CMOS Full

133