# Development of Encoder/Decoder architecture for CDMA network on chip

Nirmala Mounika<sup>1</sup>, RSVS Aravind<sup>2</sup>

Abstract- CDMA is the method to multiplex multiple codes together to transfer information over chip between different devices on the facilitated environment. It is very famous due to its high trough put and efficiency. The communication over the chip is becoming a regular problem since on chip devices should be as small as possible and they should consume less energy but practical it is odorous task. In this project we are implementing CDMA approach to the system on chip. The proposed encoder and decoder will which are occupying less area than area and it are very high speed due to the simple architecture. We are using modified orthogonal set of the Walsh and SB schemes. The schemes are designed using Verilog HDL. The design description is synthesized in Xilinx ISE14.7In encoded with an orthogonal code the transmitter module, source data from different senders are freely of a standard start and these coded data are joined by a XOR task. By then, the aggregates of data can be transmitted to their objectives through the on chip correspondence base.

# INTRODUCTION

In the authority module, a progression of chips is recuperated by taking an AND activity between the aggregates of data what's more, the relating orthogonal code. After an essential collection of these chips, remarkable data can be revamped. We execute our encoding/deciphering system and apply it to a CDMA Nook with a star topology.

With the fast development of the computational multifaceted nature, more preparing

Components (PEs) are incorporated onto a single chip, and framework on chip (NoC) has been proposed to address the flexibility, throughput, and unfaltering quality issues of on-chip correspondence. In any case, conventional package changed NoCs

encounter the evil impacts of nondeterministic transmission dormancy and obliged open entryways for parallel data trade, since different streams can't move beyond an association meanwhile. To decide these issues, the CDMA methodology as a convincing strategy for realizing world class on-chip correspondence was associated with NoCs. The as of now proposed CDMA NoCs rely upon an automated encoding and deciphering procedure requiring that the spreading codes have both the orthogonal and alter properties. To this end, the Walsh-code is usually used. Regardless, the Walsh-code-based (WB) encoding and disentangling system has trademark burdens, which are given as takes after.

1) Design Complexity: In the encoding technique, a math extension method of reasoning unit, whose basis overhead additions with the amount of senders, is used to join coded data.

Deciphering technique, a key demux-gathering balance unit is used with recuperate the source data from mixed data chips (in this compact, each bit of a spreading code is known as a chip, and along these lines the encoded data is called data chips). This unit is, in any case, an area eating up.

2) Low Code Utilization: In a S-chip Walsh-code set, S must be identical to 2N, where N is a trademark number, and at most S-1 progressions can be used to encode the main data. This results in an abuse of courses of action in the code set. For example, a 16-center sort out requirements a 32-chip Walsh-code set, in light of the fact that a 16-chip Walsh-code set can simply give 15 plans to data encoding and it in this way can't satisfy the need of 16 progressions, one for each center point. To address the beforehand said

<sup>&</sup>lt;sup>1</sup> Pursuing M.Tech (ES), Newton's Institute of Engineering College, Alugurajupally, Macherla, Guntur dist., AP, India

<sup>&</sup>lt;sup>2</sup>Associate Professor, Newton's Institute of Engineering College, Alugurajupally, Macherla, Guntur dist., AP, India

deficiencies, we propose another standard-start Based (SB)

### EXISTING SYSTEM

The Walsh code is generally used. Nevertheless, the Walsh code-based (WB) encoding and disentangling system has natural deficiencies, which are given as takes after.

# 1) Design Complexity:

In the encoding procedure, a number juggling development reason unit, whose method of reasoning Overhead augmentations with the amount of senders, is used to join coded data. In the unwinding methodology, a key de mux storing up balance unit is used with recoup the source data from mixed data chips (in this brief, each bit of a spreading code is known as a chip, and thusly the en coded data is called data chips). This unit is, in any case, district eating up.

2) Low Code Utilization: In a S chip Walsh code set, S must be comparable to 2N, where N is a trademark number, and at most S – 1 groupings can be used to encode the primary data. This results in an abuse of groupings in the code set. For example, a 16 center point sort out necessities a 32 chip Walsh code set, in light of the way that a 16 chip Walsh code set can simply give15 progressions for data encoding and it in like manner can't satisfy the need of 16 groupings, one for each center point. The already proposed CDMA NoCs rely upon an electronic encoding and deciphering strategy requiring that the spreading codes have both the orthogonal and modify properties.

## PROPOSED SYSTEM

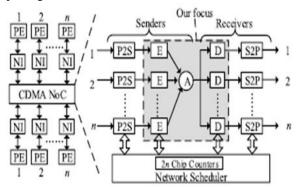

The fundamental structure of applying CDMA framework to NoC with a star topology is showed up in Fig. 1-In this figure, a PE executes assignments of the application and framework interface (NI) allotments data streams from PE into packs and reproduce data streams by using packages from NoC. In the sender, package ripples from NI are changed to a progressive piece stream by methods for a parallel to serial (P2S) module. This bit stream is encoded with an orthogonal code in the Encoding module (E in Fig. 1). The coded data from different encoding modules are incorporated into the Addition module

(An in Fig. 1). By then, the wholes of data chips are transmitted to beneficiaries. In the beneficiary, De coding modules (D in Fig. 1) reproduce one of a kind data bits from the totals of data chips. By then these progressive piece streams are changed to divide by serial-to-parallel (S2P) modules. Finally, these package vacillates are traded

Structure of CDMA NoC

### CDMA Encoder

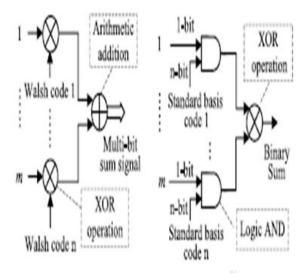

Two unmistakable encoding methods, WB encoder and SB encoder, are contemplated in Fig. 2. Fig. 2(a) exhibits the WB encoder plan. A remarkable data bit is first encoded with a Walsh code by taking a XOR assignment. By then, these encoded data are connoted a multi bit entire banner by taking arithmetical additions. Each sender needs a XOR passage,

Also, different wires are used to express the aggregate banner in case we have no less than two senders. Moreover, the amount of wires augments as the amount of senders' increases.

Block diagram of encoding scheme. (a) WB encoder. (b) SB encoder.

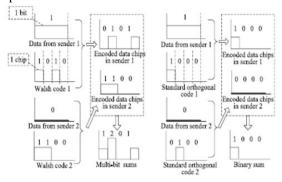

Shows our SB encoding design. A special data bit from a sender is supported into an AND entryway in a chip by chip way, and it will be spread to n chip encoded data with an orthogonal code of a standard start. The association between a bit and a chip is demonstrated then, the encoded data from different senders are joined through a XOR errand, and a combined total banner is created. Henceforth, the yield hail is constantly a progression of parallel banner traded to objective using one single wire. The developments of both the encoding designs are depicted.

Illustrates the WB encoding process with four chip Walsh codes and the SB encoding process with four chip standard orthogonal codes respectively

### CDMA Decoder

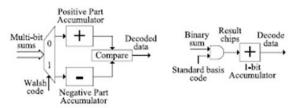

The WB deciphering plan is exhibited in Fig. 4(a). As indicated by the chip estimation of Walsh code, the got multibit aggregates are collected into positive part (if the chip esteem is 0) or negative part (if the chip esteem is 1). In this way, the two gatherers in the WB decoder independently.

Contain a multibit viper to collect the coming chips and a gathering of registers to hold the aggregated esteem. Through the examination module after the two aggregators, the original information is recreated. In the event that the estimation of positive part is substantial, the first information is 1. Something else, the unique information is 0.

Block diagram of decoding scheme. (a) WB decoder. (b) SB decoder

The SB translating plan is appeared in Fig. 4(b). At the point when the double entirety flag touches base at beneficiaries, an AND activity is taken between the twofold aggregate and the relating orthogonal code in chip by chip way.

### SIMULATION RESULT

Fig: Wash code encoding

Fig: Wash code decoding

### CONCLUSION

We propose another CDMA encoding/interpreting technique for on-chip correspondence. It can be acknowledged by utilizing straightforward rationale and expenses less power and region. The standard premise other than the Walsh code is utilized as the spreading code as a part of our strategy. It in this manner diminishes the encoding/interpreting inactivity and builds the most extreme throughput of NoCs

Numerical evidence is directed to demonstrate the rightness of our strategy. From the exploratory results, we find that our technique outflanks the WB encoding/deciphering plan, and the CDMA NoC execution is additionally enhanced when our strategy is connected.

### **REFERENCES**

- [1] Jian Wang, Zhonghai Lu, and YubaiLiA New CDMA Encoding/Decoding Method foron-Chip Communication Network IEEE Transactions On Very Large Scale Integration (Vlsi) Systems, Vol. 26, No. 6, April 2016.

- [2] A. J. Viterbi, CDMA: Principles of Spread Spectrum Communication. Reading, MA, USA: Addison-Wesley, 1996.

- [3] S. Shimizu, T. Matsuoka, and K. Taniguchi, "Parallel bus systems using code-division multiple access technique," in Proc. Int. Symp. Circuits Syst., May 2003, pp. II-260–II-263.

- [4] E. H. Dinan and B. Jabbari, "Spreading codes for direct sequence CDMA and wideband CDMAcellular

- [5] Nima Jafarzadeh, Maurizio Palesi, Ahmad, and Afzali- Kusha, —Data Encoding Techniques for Reducing Energy Consumption in Network-on-Chipl IEEE Trans. Very Large Scale Integr. (VLSI) Syst,Mar,2014.

- [6] International Technology Roadmap for Semiconductors. (2011) [Online]. Available: http://www.itrs.net

- [7] D. Yeh, L. S. Peh, S. Borkar, J. Darringer, A. Agarwal, ane w. M. Hwu, —Thousand-core chips roundtable, IEEE Design Test Comput., vol. 25, no. 3, pp. 272–278, May–Jun. 2008

- [8] M. R. Stan and W. P. Burleson, —Bus-invert coding for low-power I/O,I IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 3, no. 1, pp. 49–58, Mar. 1995.

[9] S. Ramprasad, N. R. Shanbhag, and I. N. Hajj, A coding framework for low-power address and data busses, IEEE Trans. Very Large ScaleIntegr. (VLSI) Syst., vol. 7, no. 2, pp. 212–221, Jun. 1999. [10].C. L. Su, C. Y. Tsui, and A. M. Despain, —Saving power in the control path of embedded processors, IEEE Design Test Comput., vol. 11, no. 4, pp. 24–31, Oct.–Dec. 1994.

# **AUTHOR DETAIL:**

- BUSA.NIRMALA MOUNIKA was born in Guntur, AP, India. She graduated from the Jawaharlal Nehru Technological University Kakinada. Her special fields of interest included Embedded systems & VLSI. Presently She is studying M.Tech in Newton's Institute of Engineering, Macherla

- Mr.RSVS Aravind post Graduated in M.TECH & Communications aurora in Electronics scientific technological and research academy 2007 Hyderabad to 2009 JNTUH.M.Sc Electronics in **ANDHRA** UNIVERSITY 2001 CAMPUS from to 2003 Teaching experience:12years in AEC (AURORA), ASTRA, NOVA, NEWTONS AMIE (Associate member in Institute of Engineers) enrolled on 30-09-2015.Presently working as HEAD OF THE DEPARTMENT OF ECE in Newton's Institute of Engineering, macherla