# A New Three Phase Symmetrical Multilevel Converter for Grid Connected System Using PV Source

D Rajesh<sup>1</sup>, S. Papa Rao<sup>2</sup>

<sup>1</sup>Pursuing M.Tech, PE Branch, Dept of EEE.

<sup>2</sup>Asst. Prof,EEE Dept ,Brilliant Institute Of Engineering and Technology

Abstract—in this paper a new three phase symmetrical multilevel converter for grid connected system using PV source. The renewable energy sources are application of the distributed generation (DG) in the distribution system acquired more attention .The Distribution generation systems are powered by micro sources such as fuel cells, photovoltaic (PV) systems, and batteries. PV distributed system in which the solar source is low dc input voltage interfaced to grid using front-end conversion. Three phase Cascaded H-Bridge Sevenlevel inverter is interfaced with low frequency transformer multiplePV Source is proposed. Nowadays multilevel inverter (MLI) plays a vital role in the field of power electronics and being widely used in many industrial and commercial applications. Moreover the advantages like high quality power output, low switching losses, low electro-magnetic interference (EMI) and high output voltage made multilevel inverter as a powerful solution in converter topology.

The proposed topology is suitable for any number of levels. When the levels are increased the number of switches used is reduced compared to the conventional cascaded H-bridge multilevel inverter. This paper is particularly focused on the 13-level inverter with the requirement of low switching components. In the proposed topology only 7 switches were used. The harmonic reduction is achieved by selecting appropriate switching angles. It shows hope to reduce initial cost and complexity hence it is opt for grid applications.

Index Terms—Multilevel Inverter, MATLAB, THD and PV Technique.

# I. INTRODUCTION

In photovoltaic systems, solar energy is converted into-electrical energy by photovoltaic (PV) arrays. PV arrays arevery popular since they are clean, inexhaustible and requirelittle maintenance. Photovoltaic systems require interfacing power converters between the PV arrays and the grid. These power converters are used for two major tasks. First, to ensure that the PV arrays are operated at the

maximumpower point (MPPT) [2-7]. Second, to inject a sinusoidalcurrent into the grid. Normally there are two powerconverters [8]. The first one is a DC/DC power converterthat is used to operate the PV arrays at the maxi-mum powerpoint. The other one is a DC/AC power con-vertertointerconnect the photovoltaic system to the grid. The classical single or three-phase two level voltage sour-ceinverter is normally used for this power converter type. topologies However, other have proposed.Multilevel converter topologies are a very choicefor real-izing interesting this objective. Multilevel power converters present several advantagesover a conventional two level convert-er such as: reducingswitching frequency, output voltage with very low distortion and reduced dv/dt stress. In this way, severalmultilevel topologies have been applied to photovoltaic systems.

There are several PV system configurations. Thesecon-figurations are the centralized technology, stringtechnology, multi-string technology and AC-moduletechnology.

The number and type of power converters that is used to interconnect the PV system to the grid is dependent of the technology that is used. The multistring technologyhas several different groups of PV arrays. As a consequence, the electric system cannot manage these intermittent pow-er sources beyond certain limits, resulting in RES genera-tion curtailments and, hence, in RES penetration levels lower than expected. Power electronic converters, espe-cially dc/ac PWM inverters have been extending theirrange of use in industry because they provide reduced energy consumption, better efficiency, improved quality of product, good maintenance, and so on. For a medium voltage grid, it is troublesome to connect only one power semiconductor switches directly. As a result, a

multilevel power converter structure has been introduced as an alternative in high power and medium voltage situations such as laminators, mills, conveyors, pumps, fans, blowers, compressors, and so on.

As a cost effective solution, multilevel converter not only achieves high power ratings, but also enables the use of low power application in renewable energy sources such as photovoltaic, wind, and fuel cells which can be easily interfaced to a multilevel converter system for a high power application. The most common initial applica-tion of multilevel converters has been in traction, both in locomotives and track -side static converters. More recent applications have been for power system converters for VAR compensation and stability enhancement, ac- tive filtering, high-voltage motor drive, high-voltage dc transmission, and most recently for medium voltage

induction motor variable speed drives. Many multilevel converter applications focus on industrial medium-volt-age motor drives, utility interface for renewable energy systems, flexible AC transmission system (FACTS), and traction drive systems.

The inverters in such application areas as stated above should be able to handle high voltage and large power. For this reason, two -level high-voltage and large-power inverters have been designed with series connection of switching power devices such as gate -turn-off thyristors

(GTOs), integrated gate commutated transistors (IGCTs), and integrated gate bipolar transistors (IGBTs), because the series connection allows reaching much higher voltages. However, the series connection of switch-ing power devices has big problems, namely, non equal distribution of applied device voltage across series-connected devices that may make the applied voltage of individual devices much higher than blocking voltage of the devices during transient and steady-state switching operation of devices.

As alternatives to effectively solve the above -mentioned problems, several circuit topologies of multilevel inverter and converter have been researched and utilized. The output voltage of the multilevel inverter

has many levels synthesized from several DC voltage sourc-es. The quality of the output voltage is improved as the num-ber of voltage levels increases, so the quantity of out-put filters can be decreased. A multilevel converter can be implemented in many different ways. The simplest techniques involve the parallel or series connection of conventional converters to form the multilevel waveforms. More complex structures effectively insert converters within converters. The voltage or current rat-ing of the multilevel converter becomes a multiple of the individual switches, and so the power rating of the converter can exceed the limit imposed by the individual switching devices. The proposed three phase multilevel voltage source inverter is recently applied in many indus-trial applications such as ac power supplies, static VAR compensators, drive systems, etc. One of the significant advantages of multilevel configuration is the harmonic re-duction in the output waveform without increasing switch-ing frequency or decreasing the inverter power output [5]. The output voltage waveform of a multilevel inverter is composed of the number of levels of voltages, typically obtained from capacitor voltage sources. As the number of levels reach infinity, the output THD approaches zero.

The number of the achievable voltage levels, however, is limited by voltage unbalance problems voltage clamping requirement, circuit layout, and packaging constraints. This paper proposes the three phase multilevel topology interfaced to grid by using input PV sources.

# II. H-BRIDGE MULTILEVEL INVERTER

The traditional two or three levels inverter does not com-pletely eliminate the unwanted harmonics in the output waveform. Therefore, using the multilevel inverter as an alternative to traditional PWM inverters is investigated.

In this topology the number of phase voltage levels at the converter terminals is 2N+1, where N is the number of cells or dc link voltages. In this topology, each cell has separate dc link capacitor and the voltage across the capacitor might differ among the cells. So, each power circuit needs just one dc voltage source. The number of dc link capacitors is proportional to the number of phase voltage levels .Each H bridge cell may have positive, neg-ative or zero voltage. Final output voltage is the sum of all H-

50

bridge cell voltages and is symmetric with respect to neutral point, so the number of voltage levels is odd. Cas-caded H-bridge multilevel inverters typically use IGBT switches. These switches have low block voltage and high switching frequency. Consider the seven level inverter; it requires 12 IGBT switches and three dc sources.

A cascaded H-bridge multilevel inverter is simply a series connection of multiple H-bridge inverters. Each H-bridge inverter has the same configuration as a typical single-phase full-bridge inverter. The cascaded H-bridges mul-tilevel inverter introduces the idea of using Separate DC Sources (SDCSs) to produce an AC voltage waveform. Each H-bridge inverter is connected to its own DC source Vdc. By cascading the AC outputs of each H bridge in-verter, an AC voltage waveform is produced

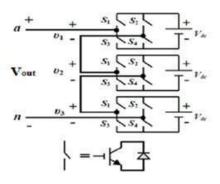

Fig 1. Cascaded H-bridge 7-level Inverter By closing the appropriate switches, each H-bridge inverter can produce three different voltages: +Vdc, 0 and -Vdc.

Fig 2. Output Voltage of cascaded H-bridge seven level inverter.

It is also possible to modularize circuit layout and packag-ing because each level has the same structure, and there are no extra clamping diodes or voltage balancing capaci-tors. The number of switches is reduced using the new to-pology. This circuit is simulated using the MATLAB soft-ware. The results are shown in the later sections in detail.

#### III. PROPOSED TOPOLOGY

The main objective is to improve the quality output volt-age of the multilevel inverter with reduced number of switches.

An important issue in multilevel inverter design is that to generate nearly sinusoidal output voltage waveform and to eliminate lower order harmonics. A key concern in the fundamental switching scheme is to determine the switch-ing angles in order to produce the voltage with fundamen-tal frequency.

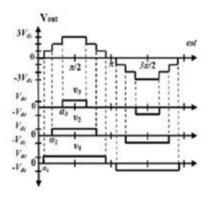

Fig 3Proposed Power circuit for 7-level output

There are three modes of operation for the proposed 7-level multilevel inverter. These modes are explained as below. Powering Mode: This occurs when both the load current and voltage have the same polarity. In the posi-tive half cycle, when the output voltage is Vdc, the cur-rent pass comprises; the lower supply, D6, Q1, load, Q4, and back to the lower supply. When the output voltage is 2Vdc, current pass is; the lower source, Q5, the up-per source, Q1, load, Q4, and back to the lower source. When the output voltage is 3Vdc, the current pass com-prises: upper supply, Q1, load, Q4, Q7, lower supply. In the negative half cycle, Q1 and Q4 are replaced by Q2 and O3 respectively. Free-Wheeling Mode Freewheeling modes exist when one of the main switches is turned-off while the load current needs to continue its pass due to load inductance. This is achieved with the help of the anti-parallel diodes of the switches, and the load circuit is disconnected from the source

terminals. In this mode, the positive half cycle current pass comprises; Q1, load, and D2 or Q4, load, and D3, while in the negative half cycle the current pass includes Q3, load, and D4 or Q2, load, and D1.Regenerating Mode In this mode, part of the energy stored in the load inductance is returned back to the source. This happens during the intervals when the load current is negative during the positive half cycle and vice-versa, where the output voltage is zero.

Fig 4 Waveforms of the proposed seven level inverter

# IV. SELECTIVE HARMONICS ELIMINA-TION

The Selective Harmonic Elimination Stepped-Waveform (SHESW) technique is very suitable for a multilevel in-verter circuit. Employing this technique along with the multilevel topology, the low Total Harmonic Distortion THD output waveform without any filter circuit is pos-sible.

A. Fourier Series and Harmonics Elimination Theory:

After applying Fourier theory to the output voltage wave-form of multilevel converters, which is odd quarter-wave symmetric, we can find the Fourier expression of the multilevel output voltage as (1). If the DC voltages are equal in the multilevel converter, the equation for the fun-damental frequency switching control method can be expressed as:

$$\begin{split} V(t) = \sum_{n=1,3,5,...}^{\infty} \frac{4V_{dx}}{n\pi} (\cos{(n\theta_1)}(\cos{(n\theta_2)} + \cos{(n\theta_3)} + \\ & \cdots + (\cos{(n\theta_z)})\sin{(nwt)} \ (1) \end{split}$$

From the equation, it can be seen that the output voltage has no even harmonics because the output voltage waveform is odd quarter-wave symmetric. It also can be seen from (2) that the peak values of these odd harmonics are expressed in terms of the switching angles  $\theta 1$ ,  $\theta 2$ , and  $\theta s$ . Furthermore, the harmonic equations produced from (2) are transcendental equations. Based on the harmonic elimination theory, if one wants to eliminate the nth harmonic, then

$$Cos(n\theta_1) + Cos(n\theta_2) + ... + Cos(n\theta_s) = 0$$

(2)

That means to choose a series of switching angles to let the value of the nth harmonic be zero. Therefore, an equa-tion with s switching angles will be used to control the s different harmonic values. Generally, an equation with s switching angles is used to determine the fundamental fre-quency value, and to eliminate s-1 low order harmonics. For an equation with three switching angles, (2) becomes

$$V(t) = \sum_{n=1,3,5,\dots}^{\infty} \frac{4V_{dc}}{n\pi} (\cos(n\theta_1)(\cos(n\theta_2) + (\cos(n\theta_s))\sin(nwt))$$

(3)

#### B. Transcendental Equations to Solve:

In this project we derived harmonic equations for elimi-nating the 3rd and 5th order harmonics. The resulting har-monic equations are

$$Cos (n\theta_1) + Cos (n\theta_2) + Cos (n\theta_3) = \frac{\pi V_1}{4V_{dc}}$$

(4)

$$Cos(3\theta_1) + Cos(3\theta_2) + Cos(3\theta_3) = 0$$

(5)

$$Cos(5\theta_1) + Cos(5\theta_2) + Cos(5\theta_2) = 0$$

(6)

To simplify the expression, (4) can be written as

$$Cos(\theta_1) + Cos(\theta_2) + Cos(\theta_3) = m$$

(7)

Where

$$M = \frac{\pi V_l}{4V_{dc}}$$

(8)

These harmonic equations (4)-(6) are transcendental equations. They are difficult to solve without using some sort of numerical iterative technique. Here

Newton Raph-son method is employed for solving these equations. C.

Solving the Harmonic Equations using Newton Raphson Method To solve the harmonic equations by resultant the-ory, they must be changed into polynomials. First, change the variables,

$$X_{1} = Cos(\theta_1)$$

(9)

$$X_2$$

-  $Cos(\theta_2)$  (10)

And

$$X_3 = Cos(\theta_3) \tag{11}$$

Also, use the following trigonometric identities:

$$Cos(3\theta) = 4cos^{2}(\theta) - 3cos(\theta)$$

12)

$$Cos(3\theta) = 3cos(\theta) - 20cos^{2}(\theta) + 10cos^{3}(\theta)$$

(13)

Then, apply them to the transcendental harmonic equa-tions above, and the following polynomial harmonic Equations can be found. For the fundamental frequency harmonic:

$$P_1(x_1, x_2, x_3) = \sum_{n=1}^{s} X_n - m = 0$$

(14)

For the 3rd harmonic:

$$P_1(x_1, x_2, x_3) = \sum_{n=1}^{s} (4X_n^2 - 3X_n) = 0$$

(15)

For the 5th harmonic:

$$P_1(x_1, x_2, x_3) = \sum_{n=1}^{s} 3X_n - 20X_n^2 + 20X_n^2 = 0$$

(16)

The polynomial equations can be solved by using the Newton Raphson method. The following are steps for solving the equations. Substitute the initial guesses for variables. Then form the jacobian matrix with Newton's formula. Repeat the same steps until the solutions to con-verge. Thus the solutions obtained are given below

$$\theta_1 = 8.70033^0$$

$\theta_2 = 28.0880^{\circ}$

$$\theta_2 = 34.9895^0$$

#### V. MATLAB/SIMULINK RESULTS:

Here simulation is carried out in different cases in that 1). Conventional Cascaded H-Bridge Multilevel Inverter 2). Proposed Symmetrical H-Bridge Multilevel Inverter 3). Proposed Three PhaseSymmetrical H-Bridge Multilevel Inverter Interfaced to Grid System with PV Source.

# Case 1: Conventional Cascaded H-Bridge Multilevel Inverter

Fig.5 Matlab/Simulink Model of Conventional Cascaded H-Bridge Multilevel Inverter Fig.5 shows the Matlab/Simulink Model of Conventional Cascaded H-Bridge Multilevel Inverter using Matlab/Simulink platform.

Fig.6 Seven Level Output Voltage Fig.6 shows the Seven Level Output Voltage of Conventional Cascaded H-Bridge Multilevel Inverter.

Fig.7 FFT Analysis of 7-Level Output Voltage Fig.7 shows the FFT Analysis of 7-Level Output Voltage of Conventional Cascaded H-Bridge Multilevel Inverter, attains 16.89%.

Case 2: Proposed Symmetrical H-Bridge Multilevel Inverter

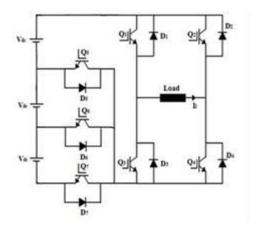

Fig.8 Matlab/Simulink Model of Proposed Symmetrical H-Bridge Multilevel Inverter

Fig.8shows the Matlab/Simulink Model of Proposed-Symmetrical H-Bridge Multilevel Inverter Fed Induction machine Drive application by using Matlab/ Simulink platform.

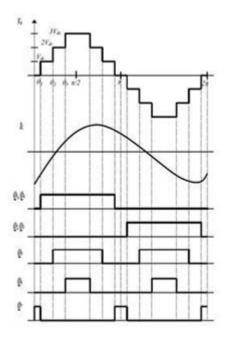

Fig.9 Seven Level Output Voltage Fig.9 shows the Seven Level Output Voltage of Proposed Symmetrical H-Bridge Multilevel Inverter.

Fig.10 Speed & Torque

Fig.10 Speed & Torque of ProposedSymmetrical HBridge Multilevel Inverter Fed Induction machine

Drive application.

Fig.11 FFT Analysis of 7-Level Output Voltage

Fig.11 shows the FFT Analysis of 7-Level Output Voltage of Proposed Symmetrical H-Bridge Multilevel Inverter, attains 16.89%. Here THD response is near to formal one, but operating under low active switches, commercially so perfect.

# Case 3: Proposed Three Phase Symmetrical H-Bridge Multilevel Inverter Interfaced to Grid System with PV Source.

Fig.12 Matlab/Simulink Model of Proposed Three Phase Symmetrical H-Bridge Multilevel Inverter Interfaced to Grid System with PV Source.

Fig.12 shows the Matlab/Simulink Model of Proposed Three Phase Symmetrical H-Bridge Multilevel Inverter Interfaced to Grid System with PV Source using matlab/Simulink package.

Fig.137 Level Output Voltage& Current Fig.13 shows the 7-Level Output Voltage&Current of-Proposed Three Phase Symmetrical H-Bridge Multilevel Inverter.

Fig.14 Grid Voltage& Current

Fig.14 shows the Grid Voltage & Current of Proposed

Three Phase Symmetrical H-Bridge Multilevel Inverter Connected to Grid by using Input PV source.

#### V. CONCLUSION

To have sustainable growth and social progress, it isnec-essary to meet the energy need by utilizing therenewable energy resources like wind, biomass, hydro, co-genera-tion, etc. In sustainable energy system, energy conserva-tion and the use of renewable source are the key para-digm. So, these new technologies of semiconductor are more suited to high power applications and they enable the design of multilevel inverters. Compared to typical PWM switching schemes, multilevel fundamental switch-ing will lead to lower switching losses. As a result, using the multilevel fundamental frequency switching scheme will lead to increased efficiency. This project presents a procedure for selectively eliminating certain harmonics in a multilevel inverter utilizing the fundamental frequency switching scheme. Newton Raphson method is presented in this paper which requires an initial guess in order to find a solution.

#### REFERENCES

- [1] AyoubKavousi, BehroozVahidi, Reza Salehi, Moham-mad azemBakhshizadeh, NaeemFarokhnia and S.HamidFathi,(April 2012) "Application of the Bee Algorithm for Selective Harmonic Elimination Strategy in Multilevel Inverters", IEEE Transactions on power electronics, vol. 27, no. 4, pp1689-1696.

- [2] DamounAhmadi, KeZou, Cong Li, Yi Huang and Jin Wang,(october 2011) "A Universal Selective Har-monic Elimination Method for HighPower Inverters", IEEE Transactions on power electronics, vol. 26, no. 10,pp2743-2752,.

- [3] FaeteFilho, Leon M. Tolbert, Yue Cao and BurakOzpineci,(September/October 2011) "Real-Time Selective Harmonic Minimization for Multilevel Invert-ers Connected to Solar Panels Using Artificial Neural Network Angle Generation",IEEE Transactions on indus-try applications, vol. 47, no. 5, pp2117-2124.

- [4] HosseinSepahvand, Jingsheng Liao and Mehdi Ferdowsi, (November 2011) "Investigation on Capaci-tor Voltage Regulation in Cascaded HBridge Multilevel Converters With Fundamental Frequency Switching", IEEE Transactions on industrial electronics, vol. 58, no. 11,pp5102-5111.

- [5] Jason R. Wells, XinGengPatrick L. Chapman Philip T. Kreinand Brett M. Nee,(January 2007)"Modulation-Based Harmonic Elimination", IEEE Transactions on power electronics, vol. 22, no. 1,pp336-340.

- [6] J. Napoles, A. J. Watson, J. J. Padilla, J. I. Leon, L. G. Franquelo, P. W. Wheeler and M. A. Aguirre, (June 2012) "Selective Harmonic Mitigation Technique for Cas-caded H-Bridge Converters with Non-Equal DC Link Volt-ages", IEEE Transactions on power electronics, pp1-9.

- [7] John N. Chiasson, Leon M. Tolbert, Keith J. McK-enzie and Zhong Du,(march 2004)"A Unified Approach to Solving the Harmonic Elimination Equations in Multi-level Converters",IEEE Transactions on power electron-ics, vol. 19, no. 2, pp478-500.

- [8] A. Maheswari, S. Mahendran, Dr. I. Gnanambal (Au-gust 2012), "Implementation of Fundamental Frequency Switching Scheme on Multi –Level Cascaded H- Bridge Inverter Fed Three Phase Induction Motor Drive" Wulfeniajournal, Klangfurt, Austria, Vol 19, No. 8, pp10-24.

### **Author Details:**

Candidate Name: DHANIYAKULA RAJESH

Pursuing M.Tech, PE Branch, Department of EEE

Brilliant Institute of Engineering and Technology, Hyderabad.

I am Dhaniyakula Rajesh, born in Nalgonda, Telangana, India in 1992. I completed my B. Tech in Electrical and Electronics Engineering in Sri Indu college of Engineering and Technology Hyderabad. I received my B. Tech degree from Jawaharlal Nehru Technology University Hyderabad in 2013. At presently doing my M. Tech degree in Power Electronics in Brilliant Institute of Engineering and Technology Hyderabad. My interested areas are Power Electronics, Power systems, Electrical machines.

# **Guide Name: S.PAPA RAO(ASST.PROF,EEE DEPT.)**,

He is a Assistant Professor in Electrical and Electronics Engineering in Brilliant Institute of Engineering and Technology. He has 4 years of teaching experience.

IJIRT 144006 INTERNATIONAL JOURNAL OF INNOVATIVE RESEARCH IN TECHNOLOGY