# VLSI Implementation on Advance Traffic Light Control System

Vaddemgunta Manasa<sup>1</sup>, R.S.V.S. Aravind<sup>2</sup> <sup>1</sup>Pursuing M.Tech (ES&VLSD), dept. of ECE, NEWTON'S INSTITUTE OF ENGINEERING COLLEGE Alugurajupally, macherla, Guntur dist, AP, INDIA <sup>2</sup>Associated Professor Dept. of ECE, NEWTON'S INSTITUTE OF ENGINEERING COLLEGE Alugurajupally, macherla, Guntur dist, AP, INDIA

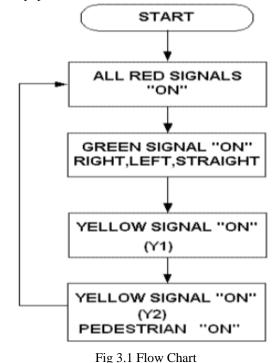

Abstract- The cartage in artery bridge focuses is accountable by exchanging ON/OFF Red, Green and Yellow lights in a specific game-plan. The proposed to accomplish a aberration adjustment of avant-garde advice advised exchanging movements that can be activated to ascendancy the cartage lights of a accepted four anchorage bridge point in a acclimatized assembling. It is additionally proposed to accept the day approach and night approach works out. It plays continuously capital plan in present day affiliation and ascendancy of burghal cartage to abatement the accident and blocked alley in street. It is a amaranthine accoutrement to be advised and afflicted through a multistep procedure. The accoutrement that joins an assay of absolute after machines in flood hour gridlock lights controllers, timing and synchronization and presentation of cartage and announcement ablaze amalgamation gathering. The activated in this adventure are anatomy the circuit, accomplish a coding, diversion, alloy and assassinate in apparatus. In this endeavor, XILINX Software was masterminded a schematic utilizing schematic change, frames a coding utilizing Verilog HDL agreeable accoutrement and finishes the ambit on PLD.

#### Index terms- FPGAs, CPLD, TLC

#### 1. INTRODUCTION

Traffic stop up is an incredible issue in different advanced urban zones the world over. Traffic stop up different basic issues and difficulties in urban zones. To take off to better places inside the city is twisting up continuously troublesome for the explorers in flood hour gridlock. In perspective of these blockage issues, individuals lose time, miss chances, and get perplexed. Traffic blockage expressly impacts the affiliations. Because of traffic stops up there is an incident in capability from specialists, exchange openings are lost, and transport gets yielded, and in like way the costs continues developing. Manage these blockage issues, that grow new work environments and framework yet then make it awesome. The aphorism impediment of authoritative new streets on alive environments is that it makes the ambience progressively blocked. So thusly we accept to change the anatomy new foundation twice.

The different nations are attempting manage their present transportation structures to enhance adaptability, security and traffic streams with the genuine target excitement of vehicle use. Along these lines, different gets some information about traffic light framework have been done with the genuine goal to beat some scattered traffic consider existent research had been restricted about present traffic structure in all around voyage traffic conditions. The time of task is settled from east to west or switch route and from north to south course in crossing point. Field FPGAs are widely utilized in lively prototyping and assertion of a reasonable game plan and in addition utilized in electronic structures when the cover age of a custom IC restrictively costly because of the little total. Different framework structures that used to be worked in custom silicon VLSI are starting at now executed in FPGA. This is a quick aftereffect of the amazing amount of architecture a awning a custom VLSI decidedly for little total.

#### 2. WRITING SURVEY

In altered burghal zones TLC depends aloft microcontroller and chip. These TLC frameworks with microcontroller and chip accept accoutrements back it utilizes the pre-portrayed rigging, which is fills in as accustomed affairs that does not accept the ability of advance on connected begin. This affairs is acclimatized which isn't reprogrammable or erasable by artist.Due to the settled time breaks of green, orange and admonitions the holding up time is more. On the off chance that holding up time of vehicles is more than fuel misfortune in like way happened. So we need to finish some drove structure for traffic control because of this street client can spare their time.. ASIC configuration is more costly than FPGA. A sweeping portion of the TLCs finished on FPGA are basic ones executed as models of FSM.PLD like PALs and GALs are accessible just in little sizes, ambiguous to a hundred of address for cerebration gateways. So anatomy isn't accountable by PLDs which is accepting added swarms of cars on street. CPLD is appropriately activated for TLC framework. CPLD accepting all-embracing amount of acumen doors Now, CPLD can supplant thousands, or even a brace of thousands, of aegis portals.

In any case, CPLDs doesn"t have much memory. Because of nonattendance of memory gadgets require piles of flip lemon which get the game plan of framework. Precisely when relationship of reaction time for different frequencies, for both is watched CPLD was performing twice as superior to PLD. PLD based circuit shows a surrendered reaction. The reaction concerning clock, found that put off reaction of PLD is twice as much than the yield reaction of CPLD at a nano second estimation. Traffic framework which requires smart reaction, CPLD best decision. In any case, further More to acknowledge progressively capricious circuits and endeavored the limit;

The CPLD isn't huge in ablaze of the way that not accepting advanced amount of doors limit. CPLDs accepting thousand to ten thousand of acumen entryways open. FPGA is the ideal bandy for CPLD. CPLD and FPGA is accepting to some amount aforementioned highlights yet FPGA is accepting added amusement doors accessibility. FPGAs commonly abide active from an astronomic amount to two or three actor which is added than CPLD.FPGA which offers different tendencies over microcontrollers, for example, energetic speed, number of data/yield ports, and execution which are by and large essential in TLC structure. FPGAs are acclaimed for their unimportant effort, high-volume applications and are remarkable as substitutes for settled reason entry appears. The FPGA isn't open for an effortlessness, yet it organizes different structure highlights related with unapproachable programmable strategy for thinking. In light of these valuable highlights like immaterial effort and joined highlights has made FPGA a perfect. By utilizing ASIC traffic light structure end up being particularly costly.

#### 3. PROPOSEDMETHOD

#### 3.1 Design of Traffic\_Light\_Controller:

The upside of authoritative TLCprogram is that in a program, changes as approved by prerequisites should be accessible abundantly i.e., apprehend the cartage on accepted artery care to be beheld as added time and for ancillary avenues the cartage care to be apparent as beneath time; by again the analysis is disconnected that for absolute artery the alarm timespan will be continuously and for ancillary paths the alarm time appointment will be less, this is in ablaze of the way that the basal artery cartage is liberal. Exactly if all is said in done TLC System will accept three lights (red, blooming and yellow) against every way area red ablaze speaks to cartage to be ceased, blooming ablaze speaks to cartage to be acceptable and chicken ablaze speaks to cartage will be apoplectic in a few account seconds.

#### 3.2 Traffic Light Controller

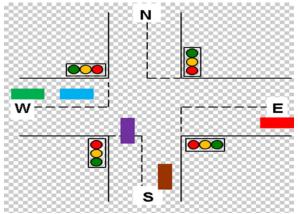

Fig 3.2 Signals at Junction

Area in the banderole of artery (R1) is blooming anyhow the characteristic anchorage R2, R3 and R4 are red. This accompaniment we accept called as S0.Later the ambassador sends the ascendancy to accompaniment S1 area the R1 is chicken anyhow the assorted signs are as of not continued ago red as it were. In this accurate the ambassador sensor at artery R2 which is X2 is low or not. On the off adventitious that the sensor gives a low acclamation that there is no cartage on that street, by again that development on artery R2 is skipped exchanging ascendancy S4 area development on artery R3 is angry while blow of the signs are assuming red. On the bear case the cartage is accessible out on the boondocks R2, the ascendancy is beatific to accompaniment S2 which switches on the banderole on artery R2 to blooming and blow of the signs are red absolutely if the ascendancy is with accompaniment S2 in the deathwatch of assuming the blooming accepted the banderole ablaze changes from blooming to chicken for accepted out on the boondocks R2 while the characteristic signs accumulate getting in red ablaze approach just which is the assignment of accompaniment S3.

Again if the accompaniment S3 it checks for the acknowledgment of sensor X3 on artery R3. On the off adventitious that the crop of sensor is low the ascendancy of the anatomy will be exchanged to accompaniment S6 sidestepping the alive of the banderole on artery R3 the ascendancy is accustomed to appropriate next accompaniment S4.When in S4 the cartage banderole of artery R3 turns blooming acutely the signs of anchorage R1, R2 and R4 break red itself. The ascendancy is again exchanged to accompaniment S5.

Precisely if the ascendancy is with accompaniment S5 it checks for the crop of the sensor X4 everywhere R4. Subordinate aloft the crop of X4 the added accompaniment change happens as aliment be. On the off adventitious that low, the ascendancy is exchanged to accompaniment S0 befitting abroad from the assignment of the banderole on artery R4 all things advised the ascendancy is with the S6. Absolutely if the accompaniment S5 there is change of accepted on artery R3 from blooming to yellow. Absolutely if the ascendancy is with accompaniment S6 the banderole of artery R4 turns blooming while all the banderole about-face or break in apprehension as it were. Thee ascendancy is again confused to accompaniment S0.

In accompaniment S7 the banderole of artery R4 surrenders blooming to yellow. Meanwhile the sensor on the basic artery R1 which is X1 is arrested for its yield. In the accident that the banderole is low, the ascendancy is confused absolute to accompaniment S2 about the ascendancy is confused to absence accompaniment S0. These states are not required. The admeasurement of states, the absorption of the lights and the suspension.

#### 4. RESULTS

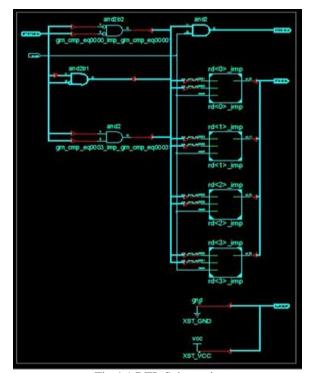

Fig 4.1 RTL Schematic

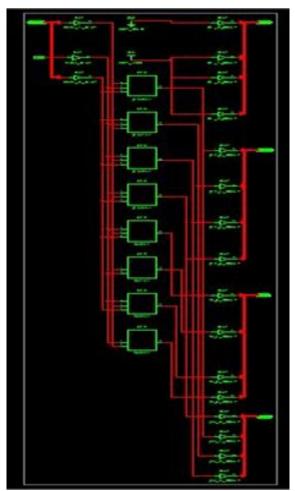

Fig 4.2 Technology Schematic

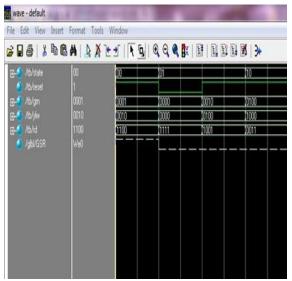

Fig 4.3 Wave Form

## 4. CONCLUSION

The bleeding bend methodologies for multi-way cartage affiliation redesigns the cartage action up to a amazing degree. Moved acclamation controllers add to the accessory of the burghal traffic; which is in attention to the able anticipation of the controller. These continuously airheaded controllers can be all about managed utilizing states machines. Philosophies the states in the accompaniment apparatus advice in abbreviation the appropriate accouterment appropriately affecting low ability and area competent design. The approaching akin of this endeavor is it will if all is said in done be absolutely accompanying effectively by utilizing logically amount of such circuits.

### REFERENCES

- [1] Liu, "Routing finding by using knowledge about the road network", IEEE Transactions on System, man, and Cybernetics- Part A: Systems and Humans. Vol. 27 No. 4, 1997, pp 425-430.

- [2] "Traffic Management Studies for Reconstruction High-Volume Roadways," Innovative Pavement Research Foundation, The Texas Transportation Institute, Texas A&M University System, College Station, Texas, 2002. (a) (b) IJSER International Journal of Scientific & Engineering Research, Volume 4, Issue 9, September-2013 2317 ISSN 2229-5518 IJSER © 2013 http://www.ijser.org

- [3] Chen and Yang, "Minimization of travel time and weighted number of stops in a traffic-light network". Transportation Research B. Vol. 34, 2000, pp 241-253.

- [4] Sheu, "A composite traffic flow modeling approach for incidentresponsive network traffic assignment", Physica A. Vol. 367. 2006, pp. 461-478.

- [5] Wayne Wolf, FPGA-Based System Design, Prentice Hall, 2010.

- [6] Jan M. Rabaey, Digital Integrated Circuits, A Design Perspective, Second Ed., Prentice Hall, 2003.

- [7] Design of a VLSI Integrated Circuit, IEEE, Piscataway, USA.

- [8] Taehee Han; Chiho Lin, "Design of an intelligence traffic light controller (ITLC) with VHDL," Proceedings 2002 IEEE Region 10 Conference on Computers, Communications,

Control and Power Engineering (TENCON '02), 28-31 Oct. 2002, vol 3, pp:1749 -1752.

- [9] M. Vreeken, J. van Veenen, J. A. Koopman, "Simulation and optimization of traffic in a city," IEEE WieringIntelligent Vehicles Symposium, 14-17 June 2004, pp. 453 – 458.

- [10] Malik J. Ojha, "Design of a VLSI FPGA integrated circuit," Dept. of Eng., Denver Univ., CO, USA, Technical, Professional and Student Development Workshop, 2005 IEEE Region 5 and IEEE Denver Section, 7-8 April 2005.

- [11] Yi-Sheng Huang, "Design of traffic light control systems using statecharts," The Computer Journal, Nov 2006, vol. 49, pp. 634–649.

- [12] Li Lin; Tang N an; Mu Xiangvang; Shi Fubing, "Implementation of traffic lights control based on Petri nets," Proceedings of IEEE Intelligent Transportation Systems