# Design of Power and Energy Efficient Approximate Multiplier in XILINX

Turaka Bhavani<sup>1</sup>, T.Ratnamala<sup>2</sup>

<sup>1</sup>Pursuing M.Tech (ES&VLSD), dept. of ECE, NEWTON'S INSTITUTE OF ENGINEERING COLLEGE, Alugurajupally, macherla, Guntur dist, AP, INDIA <sup>2</sup>Assistant Professor Dept. of ECE, NEWTON'S INSTITUTE OF ENGINEERING COLLEGE, Alugurajupally, macherla, Guntur dist, AP, INDIA

*Abstract*- Mixed media and picture handling applications, may endure blunders in calculations yet at the same time create important and gainful outcomes. This work manages a rapid inexact multiplier with TDM tree and convey forecast circuit. The changed multiplier uses an enhanced TDM convey spare tree which decreases the gadget usage on FPGA and additionally the combinational way deferral and power utilization.

## Index terms- Approximate Carry Adder, Three Dimensional Reduction method, Approximate Multiplier

#### 1. INTRODUCTION

Correct and exact models and calculations are not constantly proper for capable use in interactive media and picture preparing activities. The model of surmised count depends on totally unwinding completely correct and totally deterministic building squares while, planning vitality proficient frameworks. In computerized structures, number increase is one of the key building squares, which profoundly influences the microchip and DSP execution. A quicker advanced circuit is acquired by executing a theoretical (expectation) approach. Theoretical computerized circuits depend on quicker activity by utilizing a speculative utilitarian unit, which is a number juggling unit that utilizes an indicator for the convey motion, without really sitting tight for the convey proliferation. The theoretical unit predicts the convey of the at least one cells utilized in the advanced circuit without trusting that the genuine convey spread will happen. This is like an indicator in the microchip. Here we have considered a theoretical multiplier which comprises of a prescient convey spare decrease tree utilizing three stages: fractional items recoding, partial item dividing and theoretical pressure. The theoretical tree use (m: 2) counters, and are quicker than customary blowers dependent on half adders and full adders. The tree is additionally included a quick convey engender snake and a mistake amendment circuit. Theoretical multipliers have higher speed contrasted with their ordinary partners.

#### 2. PREVIOUS WORKS

The rough circuits have higher execution when contrasted with exact rationale circuits. Numerous estimated multipliers have been proposed in the writing [4] [6] [7] [13]. These plans utilize a truncated duplication strategy. In [6], an estimated cluster multiplier is utilized, by overlooking chosen slightest noteworthy bits in fractional items. An estimated multiplier with amendment steady has been proposed in [13]. A variable rectification consistent vague multiplier is proposed in [4]. This technique adjusts the remedy term as indicated by section n-k-1. In the event that incomplete items in segment n-k-1 are one, adjustment factor is expanded and, if every single partial item in the above segment are zero, the revision factor is diminished. In [7], an essential 2x2 multiplier square is recommended for developing bigger multiplier exhibits. In every one of these plans the zone was observed to be high. In [11] another inexact multiplier with two estimated [4:2] blower has been proposed. This multiplier requires lesser zone when contrasted with multipliers utilizing truncation procedure anyway the mistake rate was observed to be high.

[12] Describes another surmised multiplier structure which uses forecast units for the convey flag and

furthermore has lesser blunder rate when contrasted with [11]. SFUs (Speculative Functional Units) are forecast circuits that can be considered as discovery substances which are quicker than their non theoretical partners, freely of the specific execution [8]. Thus estimated multipliers utilizing SFUs likewise mean to accomplish defer upgrades, in the meantime presenting less power and region overheads. This multiplier uses Carry Save Adder (CSA) tree [14] for incomplete item decrease, wherein the convey yields are engendered instead of being safeguarded accordingly diminishes the postponement. Prevalent CSA plans incorporate Wallace tree and Dadda multiplier. Wallace tree [1] [9] result in long and sporadic wires along the segments to interface with the CSA. The wire capacitance thusly expands the deferral and vitality of the multiplier and the wires are hard to format. Dadda refined Wallace's technique by presenting a counter position methodology that requires few quantities of counters in the decrease arrange however at the expense of bigger Carry proliferate Adder (CPA) [2] [9]. The deferral from a contribution to a yield in a full snake isn't the equivalent. This deferral is subject to a specific progress (0-to-1, 1-to-0). Thusly it is additionally conceivable to concoct diverse acknowledge of a full adder wherein a particular flag way is favored regarding the others and has been structured so that a flag proliferation of this way takes a negligible measure of time [3]. The CSA plot which deals with this postponement experiencing significant change is Three Dimensional Scheme [3], where fractional item exhibit is spoken to in existence. This is trailed by a theoretical snake [5].

#### 3. PROPOSED METHOD

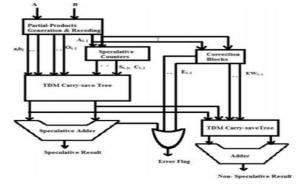

Fig. 1. Architecture of Approximate Multiplier

3.1 Partial Product Recoding

Consider two partial items aibj and ajbi of the i+j-th section of the PPM. Presently we will characterize two adjusted incomplete items:

- Ai, j = aibj AND ajbi (1)

- Oi, j = aibj OR ajbi (2)

In this way couple of incomplete items aibj and ajbi can be supplanted with changed partial items Ai, j and Oi, j. The upside of presenting such a recoding method is the presentation of lower likelihood terms in the PPM. The likelihood of Ai, j is given by (.25)2 = 0.0625, much lower than the likelihood of the first fractional item (i.e. 0.25). On the other hand the likelihood of Oi, j is 7/16. From the over two perceptions it very well may be inferred that theoretical convey tree uses bring down likelihood terms, to limit the likelihood of misprediction. The presentation of recoded terms does not change the aggregate number of partial items, but rather presents an extra little deferral for the recoded incomplete items. The figure underneath demonstrates a 16 X 16 Partial Product Matrix (PPM) subsequent to being recoded.

## 3.2 Partial Product Partitioning

Just the lower likelihood terms Ai, j is has been included the hypothesis convey spare tree. Fractional items that have a place with the biggest sections of PPM are independently recoded. In the figure given underneath the partial items in the sections 11, 12... ... 22 are recoded.

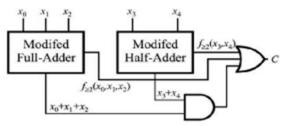

## 3.3 Speculative Compression

In spite of the fact that the likelihood Ai, j has been diminished as for the genuine incomplete items, basic evacuation of Ai, j terms would achieve a huge misprediction blunder likelihood. Therefore, rather than precluding these terms we entirety them in a rough way by utilizing theoretical blowers. A (m: 2) theoretical counter has m inputs (x0.....xm-1) and just two yields Sum (S) and Carry (C). The theory blower checks the quantity of info bits and decides the yield bits, on the supposition that not than in excess of three sources of info are high. Comparably to full adders and half adders, the yield C has a multiplied weight as for S, with the goal that 2C + S $= x0 + x1 \dots + xm - 1$  for:  $x0 + x1 \dots + xm - 13$ , it isn't conceivable to speak to total  $x0 + x1 \dots$ ..+.xm-1, by utilizing just C and S signals for all feasible info designs. The theory counter registers the

yields dependent on the supposition that not in excess of three information sources are high: If this rule isn't met, a mistake happens; the duplication result isn't right and should be amended.

Fig. 2.Speculative Compressor

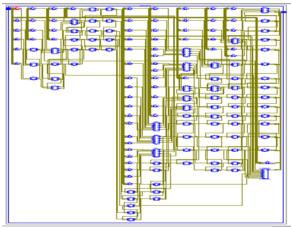

# 4. SYNTHESIS AND SIMULATION RESULTS

Fig. 3.RTL Schematic

| Device Utilization Summary (estimated values) |      |           |             |     |  |  |  |

|-----------------------------------------------|------|-----------|-------------|-----|--|--|--|

| Logic Utilization                             | Used | Available | Utilization |     |  |  |  |

| Number of Slices                              | 88   | 960       |             | 9%  |  |  |  |

| Number of 4 input LUTs                        | 155  | 1920      |             | 8%  |  |  |  |

| Number of bonded IOBs                         | 32   | 108       |             | 29% |  |  |  |

| Fig. 4.Design | Summary |

|---------------|---------|

|---------------|---------|

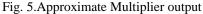

| Name        | Value | 0 ns |     | 200 ns | 11222 | 400 ns | 1600 ns | 1,000.000 ns |

|-------------|-------|------|-----|--------|-------|--------|---------|--------------|

| ▶ 😽 p[15:0] | 14000 | 0    | 900 | 3105   | X     |        | 14000   |              |

| ▶ 📢 a[7:0]  | 250   | 0    | 25  | 45     | X     |        | 250     |              |

| ▶ 👹 b[7:0]  | 56    | 0    | 36  | 69     | χ     |        | 56      |              |

|             |       |      |     |        |       |        |         |              |

## 5. CONCLUSION

Here a rapid rough multiplier configuration has been proposed. Proposed configuration uses an upgraded TDM tree. The circuit uses a portion of the incomplete item and in addition a theoretical pressure tree to whole the recoded fractional items. A

theoretical adder is utilized in the last convey engender expansion. The structures usefulness have been confirmed utilizing Xilinx ISE plan suite 14.5 (web-release). An examination of the proposed structure with customary inexact multiplier demonstrated that it has quicker task. The combination and recreation results demonstrated that the proposed multiplier configuration gives 45.4% enhancement in postponement, lesser asset usage and lesser power utilization when contrasted with multiplier without improvement. In situations where multiplier speed isn't basic, the utilization of theoretical units stays unjustified. The execution of the rough multiplier can additionally be enhanced by considering couldn't care less conditions and further by utilizing variable inertness snake rather than relatively amend adder.

# REFERENCES

- [1] L. S. Wallace, —A proposal for quick multipliers, IEEE Trans.Comput., vol. EC-13, Feb. 1964, pp. 14–17.

- [2] L. Dadda, —Some plans for parallel multipliers, Alta Frequenza, vol. 34, Mar. 1965.

- [3] V. G. Oklobdzija, D. Villeger, and S. S. Liu, —A technique for speed improved halfway item decrease and age of quick parallel multipliers utilizing an algorithmic approach, IEEE Trans. Comput., vol. 45, no. 3, Mar. 1996, pp. 294– 306.

- [4] E. J. Ruler and E. E. Swartzlander, Jr., —Data subordinate truncated plan for parallel multiplication, in Proceedings of the Thirty First Asilomar Conference on Signals, Circuits and Systems, 1998, pp. 1178–1182.

- [5] A. Cilardo, —A new theoretical expansion design appropriate for two's supplement operations, l in Proc. Structure, Autom., Test Eur. Conf. Exhib., Apr. 2009, pp. 664–669.

- [6] H.R. Mahdiani, A. Ahmadi, S.M. Fakhraie, C. Lucas, —Bio-Inspired Imprecise Computational Blocks for Efficient VLSI Implementation of Soft-Computing Applications, I IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 57, no. 4, April 2010, pp. 850-862.

- [7] P. Kulkarni, P. Gupta, and MD Ercegovac, —Trading exactness for power in a multiplier

architecturel, Journal of Low Power Electronics, vol. 7, no. 4, 2011, pp. 490-501.

[8] A. A. Del Barrio, S. O. Memik, M. C. Molina, J.M.Mendias, and R. Hermida, —A appropriated controller for overseeing theoretical useful units in abnormal state synthesis, IEEE Trans. Comput.- Aided Design Integr. Circuits Syst., vol. 30, no. 3, Mar. 2011, pp. 350–363.