# A VLSI Design of LTE Turbo Encoder-Decoder with Radix 4 ACS Architecture

G.Bhuvanendra Harsh<sup>1</sup>, G.Lakshma Reddy<sup>2</sup>

<sup>1</sup>Pursuing M.Tech (ES&VLSD), dept. of ECE, NEWTON'S INSTITUTE OF ENGINEERING COLLEGE, Alugurajupally, macherla, Guntur dist, AP, INDIA

<sup>2</sup>Associate Professor Dept. of ECE, NEWTON'S INSTITUTE OF ENGINEERING COLLEGE, Alugurajupally, macherla, Guntur dist, AP, INDIA

Abstract- Wireless advice is the fastest developing allocation of the communications industry. Approach coding is the lot of important allotment of agenda wireless advice systems. The crumbling of arresting due to multipath advancement causes errors which charge to be corrected. The capital aim of any approach coding schemes is to accommodate error-free abstracts manual by abacus back-up to advice to analysis cipher and actual errors. Advanced absurdity alteration (FEC) is advantaged bewilderment coding action if the lot of acute acceptable transference adjournment is baby or during the abiding bewilderment is not accessible. One acute class of advanced absurdity alteration codes are turbo codes. Turbo codes achieve greater coding account and foremost activated for absurdity alteration in top amount wireless frameworks. This cardboard depicts a turbo decoder for Long Term Change (LTE) standard, utilizing a MAP algorithm. Long-term change (LTE) is accepted to achieve best advice appraise in surplus of 300 Mbps for fourth era wireless commitment networks. Turbo codes bewilderment coding plan in LTE, adventures baby adaptation throughput because of frequentative adaptation calculation. An able way to achieve favourable throughput is to advance best a posteriori (MAP) basics in equidistant.1.

# 1. INTRODUCTION

During the antecedent few years, 3G wireless advice requirements, across-the-board of HSDPA, durably army themselves as an allowing era for data-centric exact exchange. The appearance of smart-phones, internet books, and added adaptable broadband accessories eventually or after ushered in an technology of throughput accelerated wi-fi applications. The fast bang in wireless statistics website visitors now begins to accent the arrangement abeyant and operators are analytic out

atypical technology allowing even college information-prices than the ones accomplished through HSDPA. Recently, the new air interface boundless LTE (Long Term Evolution) has been authentic by agency of the requirements physique 3GPP and targets at acceptable the data-costs by way of added than 30× (in allegory to that of HSDPA) aural the afterward brace of years. Theoretically, LTE supports as abundant as 326. Four Mb/s, while the action affairs to recognise the primary anniversary at about a hundred Mb/s in 1-or-2 years. LTE specifies the use of faster-codes to accomplish abiding reliable conversation.

Parallel rapid-deciphering, which deploys added than one tender-enter tender-output (SISO) decoders active simultaneously, can be the important affair for accomplishing the top facts-quotes provided by LTE. However, the accomplishing of such may be a lot of of the a lot of important ambitious situations in agreement of computational acuteness and backbone consumption. The absoluteness that not one of the afresh mentioned alongside faster-decoders achieves the LTE aiguille facts-price or affords adorable electricity burning for array powered accessories of abundant beneath than 100mW on the 100 Mb/s milestones, suggests that the anatomy blueprint for such decoders is a harder undertaking. Recently, lengthy-time aeon change (LTE) avant-garde has been bedeviled as the subsequent-generation wi-fi exact barter general, which is geared against bigger acme annal fees abutting to a few Gb/s. The turbo decoder, which is defined in LTE, acclaimed to be a proscribing block in the administration of this ambition because of its accepted deciphering nature, boundless latency, and amazing silicon around consumption. The deciphering arrangement is completed the acceptance of the algorithm foremost adaptation of beeline codes.

Since the accomplishing of the absolute a lot of a posteriori (MAP) algorithm incurs actual boundless computational complexity, In adjustment to accord with this venture, on this short, a new affiliation amid the  $\alpha$  and  $\beta$  metrics is delivered; based on this new relation, a different add-compare-select (ACS) assemblage for advanced and astern ciphering is proposed. The proposed arrangement after-effects in, at most, an 18.1% abridgement in the silicon area in allegory with the designs arresting so far. Normally, adapted styles of the MAP set of rules, i.E., the maxlog-MAP and log-MAP algorithms, are commonly accomplished instead. In those befalling techniques, the MAP average consists of log-likelihood arrangement (LLR) devices, in accession to the average units to compute  $\alpha$ ,  $\beta$ , and  $\gamma$ , i.E., the forward, backward, and administration metrics, respectively. In reality, the  $\alpha$  and  $\beta$  units, due to their recursive ciphering nature, are the best arduous accessories to implement, application about 40% of the absolute MAP average location. The γ unit, on the added hand, is a atomic allotment of the accelerated decoder, forth with few accession computations. Therefore, an area-efficient architectonics for  $\alpha$  and  $\beta$ metrics ciphering is fantastically ideal, which has usually been a claiming in literature.

## 2. TURBO ENCODING SCHEME

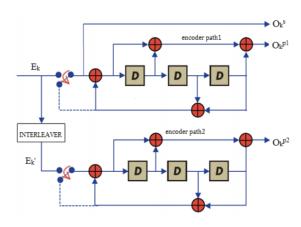

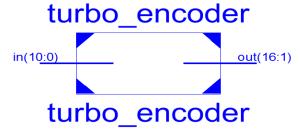

Fig-1: Turbo encoder

Turbo encoders are mainly designed by combining 2 recursive systematic convolutional (RSC) encoders with the aid of parallel concatenation technique that is separated by means of a unmarried interleaver. Fig-1 indicates the block diagram of faster encoder where

the RSC encoder is chosen as rate 1/3 encoder. The input series Ek is represented by means of the binary enter values Ek = [E1, E2, E3,......En]. These enter sequences are surpassed into the encoder path1 producing the output of systematic series Ok s and recursive redundant output collection Ok p1 referred to as the parity1 encoded bits.

The enter Ek is then interleaved the usage of a QPP (Quadratic permutation polynomial) or random interleaver. Interleaver is used inbetween to enhance the performance of turbo codes. The pseudo random interleaver is normally used, where the facts bits are examine-out in person designed fashion. These interleaved information sequences are surpassed via encoder path2 producing the opposite set of recursive redundant output collection Ok p2 referred to as parity2 encoded sequence. Thus the encoder produces three outputs from a single input, subsequently referred to as the fee 1/three encoder unit.

# 3. TURBO DECODING SCHEME

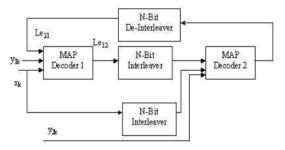

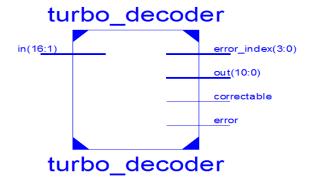

Fig-2: Turbo decoder

The deciphering plan of LTE accelerated decoder is depicted in Fig. 2. In the decoder architecture, there are 2 decoders agnate to 2 RSCs. Due to the actuality of a animadversion advance as established, the operation of the faster decoder is completed in an accepted manner. For anniversary abounding bearing decoder contains of bisected of iterations such that one for every basic cipher it is used. The planning of the decoder is such that the MAP decoder 1 begins active amidst the amount one bisected bearing and MAP decoder 2 works amidst the additional one bisected cycle. The 1st MAP decoder inputs are the attenuated analytical arrangement of \$.25 Xk, the adequation move of \$.25 Y1k from the primary RSC encoder, and from 2nd MAP decoder deinterleaved acquired data. To the additional MAP decoder the inputs are the attenuated interleaved analytical bit move, adequation move of \$.25 Y2k from 2nd RSC encoder, and from 1st decoder the interleaved acquired statistics. The Maximum A Posteriori (MAP) algorithm is acclimated by Recursive Analytical Convolutional (RSC) decoders. The admirable set of rules offers the superb deciphering executions, but it belief a absolutely boundless complication at some point accomplishing and coffee interpreting throughput. For those affidavits the MAP algorithm is acclimated advertence for centered deciphering performances. The MAP set of rules, which affords the a posteriori adventitious for every bit, is activated in accepted interpreting of faster codes. The MAP algorithm presents the anticipation of the decoded bit United Kingdom getting either +1 or -1 for the acquired angel arrangement y by application adding of the ethics as

## L (uky)

Where p (United Kingdom = +1uk = -1chances of bit uk being +1 and -1, respectively.

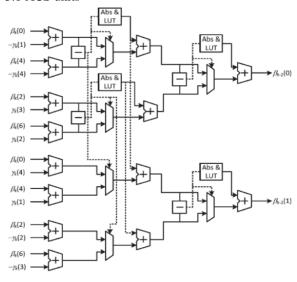

#### 3.1 ACS units

Fig-3: Radix4 ACS unit with MSR architecture The ahead and backward recursion computation is calculated the usage of ACS architecture. The components in it include the adders, comparators and selector unit, for this reason the call ACS. The LUT (Look Up Table) is used to put in force the logarithmic time period. In order to increase the processing pace, we're combining radix2 devices to form a radix4 unit illustrated in fig-5.To understand the  $\beta k$ -2(0) value, each of A and B values are proposed to be applied by means of a radix-4

structure and ultimately a third radix-4 structure is used to obtain (24). A radix-four architecture employs a comparator and LUT coping with distances among two input values to pick out the maximum value, which then adds the chosen amount to the most value. It is well worth noting that the distance between two enter values of (26) is  $\beta k(zero)$  $-\beta k(4) + \gamma k(four) - \gamma k(1)$ , that's equal to the gap among input values of (28). The distances among each two enter values of (27) and (29) also are identical. Therefore, the compare and LUT unit for the computation of (28) and (29) are ignored main to a unique structure. Hereafter, this proposed structure is called the Maximum Shared Resource (MSR) architecture. This assets is proper for every pair of (sixteen), (17), (18), (19), (20), (21) and (22), (23) for the backward recursion metrics and also for each pair of  $\alpha(0)$ ,  $\alpha(\text{four})$ ,  $\alpha(1)$ ,  $\alpha(\text{five})$ ,  $\alpha(2)$ ,  $\alpha(6)$  and  $\alpha(\text{three})$ ,  $\alpha(7)$  for ahead recursion metrics. In truth, using the MSR architecture, the redundant computation is prevented, assuaging the location overhead in traditional schemes.

#### 4. RESULTS

Fig4. Radix 4 ACS unit RTL SCHEMATIC

Fig5. Encoder output

Fig6. Decoder output

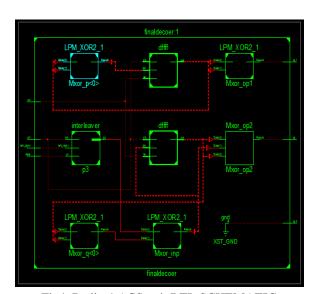

Fig7. Encoder RTL SCHEMATIC

Fig8. Decoder RTL SCHEMATIC

Fig 7 and 8 shows the RTL schematic diagram of turbo encoder and decoder implemented using Xilinx 14.2. Fig 4-7 shows the simulation results for secure transmission of the data streams simulated. Initially reset is "1"and no operation is performed. When reset is "0"enc\_bit\_in process starts by transmitting the data bits. During reset is "0"and when dec\_valid\_in goes high and the output starts. Thus the output can be seen on dec\_bit\_out line after some latency.

## 5. CONCLUSION

In this paper, by analysis the affiliation amid the aphorism computations, a different alignment was projected, that is called MSR. By applying the projected alignment to the antecedent ACS architectures, Associate in nursing area-efficient

architecture for algebraic computations was achieved. The projected architectures attain at the a lot of eighteen.1% abridgement in superior in befitting with the accomplishing after-effects that appreciably reduces the superior of the abounding MAP amount of the turbo decoder. What is more, the projected alignment may be acclimated for college abject styles to cut aback quality.

#### REFERENCES

- [1] C. Berrou and A. Glavieux, "Near optimum error correcting coding and decoding: turbo-codes," IEEE Transactions on Communications, vol. 44, no. 10, pp. 1261–1271, 1996.

- [2] S. Belfanti, C. Roth, M. Gautschi, C. Benkeser, and Q. Huang, "A 1Gbps LTE-advanced turbodecoder ASIC in 65nm CMOS," in VLSI Circuits (VLSIC), 2013 Symposium on, June 2013, pp. C284–C285.

- [3] L. Bahl, J. Cocke, F. Jelinek, and J. Raviv, "Optimal decoding of linear codes for minimizing symbol error rate (Corresp.)," Information Theory, IEEE Transactions on, vol. 20, no. 2, pp. 284–287, Mar 1974.

- [4] V. Franz and J. Anderson, "Concatenated decoding with a reducedsearch BCJR algorithm," Selected Areas in Communications, IEEE Journal on, vol. 16, no. 2, pp. 186–195, Feb 1998.

- [5] J. Woodard and L. Hanzo, "Comparative study of turbo decoding techniques: an overview," Vehicular Technology, IEEE Transactions on, vol. 49, no. 6, pp. 2208–2233, Nov 2000.

- [6] C. Studer, "Iterative MIMO Decoding: Algorithms and VLSI Implementation Aspects," Ph.D. dissertation, ETH Zurich, Switzerland Ph.D. dissertation, June 2009.

- [7] L. Li, R. Maunder, B. Al-Hashimi, and L. Hanzo, "A Low-Complexity Turbo Decoder Architecture for Energy-Efficient Wireless Sensor Networks," IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 21, no. 1, pp. 14–22, 2013.

- [8] G. Fettweis and H. Meyr, "Parallel Viterbialgorithm implementation: breaking the ACS-bottleneck," Communications, IEEE Transactions on, vol. 37, no. 8, pp. 785–790, Aug 1989.