# RAM Enabled Built in Self Test (BIST) for VLSI Circuits using Verilog

Boini Naresh<sup>1</sup>, Parigi Sai Chandana<sup>2</sup>, Dr.Md.Salauddin<sup>3</sup>(Guide)

<sup>1,2,3</sup> Department of Electronics and Communication Engineering, J.B. Institute of Engineering & Technology, (UGC Autonomous, Permanently Affiliated to Jawaharlal Nehru Technological University, Hyderabad), Bhaskar Nagar (Post), Moinabad Mandal, R.R. Dist.-500075, 2021-2022

Abstract— Because of the fast size of combination in Integrated circuit plans which has reached submicron innovations, testing has developed to be a basic variable. Configuration engineers who don't plan frameworks in light of full testability open themselves to the expanded chance of item disappointments and botched market open doors. In such a situation where ordinary testing approaches are frequently ineffectual and lacking, BIST has demonstrated its worth. BIST is a plan method that permits a circuit to test itself. In this task the test execution accomplished with the execution of BIST is demonstrated to be sufficient to balance the disincentive of the equipment upward created by the extra BIST hardware. The strategy can give more limited test time contrasted with a remotely applied test and permits the utilization of minimal expense test hardware during all phases of creation. The idea was planned and executed with Xilinx ISE 14.2.

Index Terms: LFSR, MISR, BIST controller.

#### **I.INTRODUCTION**

Testing assumes an essential part underway and bundling of all purchaser products for this situation VLSI circuits. A ware must be tried and confirmed OK by the maker before it is delivered to a buyer. Anyway testing of VLSI parts is undeniably more unique and muddled as for other shopper products. As the size of Integration rises quickly the intricacy of circuits additionally rises dramatically where testing strategies are likewise compelled to become undeniably more intricate. Testing of an ordinary VLSI circuit mostly includes utilization of test vectors to the Circuit under Test (CUT) and Analyzing the reaction. Under ordinary circumstances, a hardware like ATE (Automatic Test Equipment) is utilized for these reasons. Anyway the cumbersomeness of the gear alongside time limitations have demonstrated them to be an

obligation instead of a resource. In this setting we propose through this paper an Automatic On-Chip testing system Built in Self-Test curtailed as BIST which is an innovation whose future degree stretches out to Self-Healing and other constant applications that includes top of the line blunder identification and testing.

A.Why is Digital Testing Important?

The term Digital Testing is characterized as "testing a computerized circuit to check that it preforms the predetermined rationale capacities in legitimate time."[1]. There are a few central contrasts that make VLSI circuit testing more significant stage to guarantee quality, contrasted with old style frameworks which incorporates the accompanying,

1) The chip execution has developed to sub-micron advancements coordinating great many trasistors and the speed of activities has crossed paces of GHz. This has additionally brought about fittings with extremely high complexities. Evidently, with additional degrees of combination there is plausible of more number of faults. Just when an innovation develops and blames will generally diminish, another innovation in light of lower sub-micron gadgets advances, consequently continuously continuing to test issues dominant.[1]

2)In instance of location of flaws in a conventional framework it is analyzed and fixed Nonetheless in

framework it is analyzed and fixed. Nonetheless, in the event of circuits, on identification of a shortcoming the chip is binned as damaged and rejected (i.e., not fixed). All in all, in VLSI testing chips are to be binned as ordinary/broken so that main shortcoming free chips are delivered and no fixing is expected for defective ones.[1].

## B.Why BIST?.

ATE or Automatic Test Equipment is one among the traditionally utilized testing instruments. A few

disadvantages of ATEs are redressed or improved through the execution of BIST. These incorporate, diminished testing and upkeep cost, decreased cost of Automatic Test design Generator (ATPG), decreased capacity and support of test designs, Capability of testing numerous units in equal, more limited test application times and the capacity of the framework to test at utilitarian frameworks velocities and lessening the massiveness of the systems.[2]

## II.BIST ARCHITECTURE

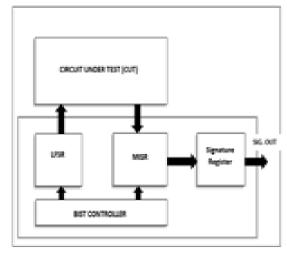

The fundamental BIST engineering requires the expansion of three equipment blocks to a computerized circuit: a test design generator, a reaction analyzer, and a test regulator. The test design generator generates the test designs for the CUT which is a Linear Feedback Shift Register LFSR, the reaction analyzer is a Multiple Input Signature curtailed as MISR and the BIST regulator which controls the LFSR and the MISR by making Necessary choices on what the piece length ought to be as per the CUT. The essential engineering is displayed in Fig 1.

Fig.1 BIST ARCHITECTURE

#### A.PATTERN GENERATOR or LFSR

Test Pattern Generator(TG) and Response Monitor(RM) are much of the time executed by basic, counter-like circuits, particularly direct criticism shift registers (LFSRs). The LFSR is ann-bit shift register which pseudo-arbitrarily looks between 2*n*-1 qualities. It is a shift register framed from standard flip-flops, with the results of chosen backpeddles being taken care of back (modulo-2) to the

shift register's bits of feedbacks. Like a paired counter, all 2n-1 states are created, yet all the same in a "irregular" request that is repeatable. The elite OR doors and shift register act to create a pseudorandom double succession (PRBS) at every one of the flipflop yields. By accurately picking where we take the criticism from a n - bit shift register we can deliver a PRBS of length 2n-1, a maximal-length grouping that incorporates every single imaginable example (or vectors) of n bits, barring the each of the zeros pattern. The every one of the zeros case is unimaginable in this sort of LFSR since, in such a case that the seed is every one of the 0 state, then the LFSR will be stuck at each of the 0 state as the criticism rationale is XOR gates.[3]

When utilized as a TG, a LFSR is set to spin quickly through an enormous number of its states. These states, whose decision and request rely upon the plan boundaries of the LFSR, characterize the test designs. In here we utilize the rule of Pseudo Random Pattern generation.[2]. A line of 0's and 1's is known as a pseudo-irregular double grouping when the pieces have all the earmarks of being arbitrary in the nearby sense, yet they are in someway repeatable. This design type, be that as it may, has the potential for lower equipment and execution overheads and less plan exertion than the first techniques. In pseudorandom test designs, each piece has a roughly equivalent likelihood of being a 0 or a 1[2].

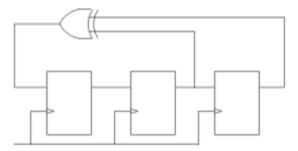

For the simplicity of understanding we plan a 3 bit LFSR given by the polynomial equation  $x^3 + x^2 + 1$ .

Fig 2 3-cycle LFSR [3]

The criticism is done as such as to make the framework more steady and liberated from mistakes. Explicit taps are taken from the tapping focuses and afterward by utilizing the XOR procedure on them they are criticism into the registers. The maximal length succession of a 3 digit LFSR has been given in the accompanying table 1.

| Table | 1Maximal-length | succession | for | the | 3-cycle |

|-------|-----------------|------------|-----|-----|---------|

| LFSR[ | [3]             |            |     |     |         |

| Clock | $Q0_{t+1} =$        | $Q1_{t+1}$ | $Q2_{t+1}$ | Q0Q1Q2 |

|-------|---------------------|------------|------------|--------|

|       | $Q1_t \oplus +Q2_t$ | $=Q0_t$    | $=Q1_t$    |        |

| 1     | 1                   | 1          | 1          | 7      |

| 2     | 0                   | 1          | 1          | 3      |

| 3     | 0                   | 0          | 1          | 1      |

| 4     | 1                   | 0          | 0          | 4      |

| 5     | 0                   | 1          | 0          | 2      |

| 6     | 1                   | 0          | 1          | 5      |

| 7     | 1                   | 1          | 0          | 6      |

| 8     | 1                   | 1          | 1          | 7      |

## **B.RESPONSE ANALYZER or MISR**

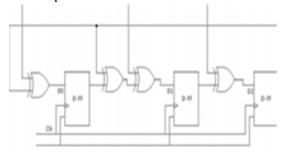

A MISR or Multiple Input Signature Register plays out the mark examination in the framework. Signature investigation is significant on the grounds that great and defective circuits create various marks. The mark values are contrasted eventually with confirm assuming the CUT is to be ensured tried OK. The Pseudo-Random Pattern Generator produces the vital examples which are taken care of as contributions to the CUT. The reaction of the CUT is taken care of to a MISR. The MISR compacts all results into one LFSR subsequently diminishing how much equipment expected to pack a different bit stream. There are several ways to interface the contributions of LFSRs to shape a MISR. Since the XOR activity is straight and cooperative,  $(A \oplus B) \oplus C$ = A

$\oplus$   $\circ$  (B  $\oplus$   $\circ$  C), as long as the after effect of the augmentations are similar then the various portrayals are same. Assuming we have a n - chomped long MISR we can oblige up to n contributions to frame the mark [3]. MISR can be created utilizing the comparable condition utilized on account of a LFSR for example x3 + x2 + 1.

Fig 3 .MISR with 3 info and 3 result bits [3]

#### C.CIRCUIT UNDER TEST

The circuit under test is the test circuit which is set for testing. At first a completely working circuit is put in the chip attachment which is put off-chip concerning the parent chip lodging the LFSR, MISR, Signature register and the BIST regulator. When there is a need of testing the expected hardware is associated with the parent chip and is run.

#### D.BIST CONTROLLER

The Controller controls the LFSR and the MISR as per the detail of the CUT. LFSRs and MISRs of fundamental piece sizes are now put away in the LFSR and MISR segments. Prior to interfacing the CUT the quantity of information sources and results of the CUT are indicated. Appropriately the Controller calls the necessary piece measured LFSR and MISR.

### E.SIGNATURE REGISTER

The Signature register stores signature values produced by the MISR. At last by looking at the mark esteem produced by a decent and broken circuit are contrasted with confirm f the CUT is great or defective.

#### III.HOW THE SYSTEM WORKS?

The Clock and reset inputs are given as contribution to the parent chip. The vital piece lengths are likewise given as contributions to the Controller. A flawless circuit is set at first instead of the circuit under test. The framework is run and a mark esteem is produced for the circuit. One more circuit of a similar kind say a broken circuit-is given at the CUT and the framework is run. Another mark esteem is produced. On the off chance that the mark upsides of both the circuits coordinates, the CUT is impeccable. Going against the norm in the event that they don't match then it is obvious that there is a shortcoming present in the recently presented circuit.

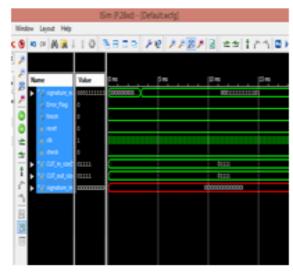

## A. Reproduction Results

1)The reproduction results for getting the mark esteem keeping the check esteem =0 and running the usefulness circuit has been given underneath in fig 4.The outcome for check esteem =1 running the test circuit to confirm in the event that the mark esteem is equivalent to in fig 4 is outlined in fig 5.

Fig 4

Fig 5.

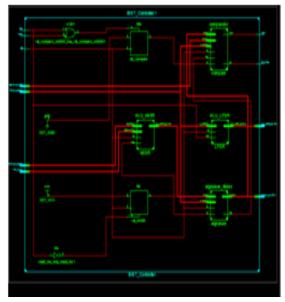

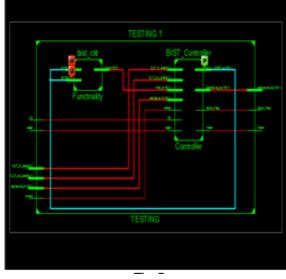

The RTL schematic of the entire testing block is shown in Fig. 6 and that of the BIST controller alone is shown as per the fig 7.

Fig 6.

Fig 7

## IV.ACKNOWLEDGMENT

We are deeply grateful to Mr.Agi Joseph George, Mr. Binu.C.Pillai and Mr. Ajai Mathew who gave us guidance and suggestions and helped us in the successful completion of this project.

# REFERENCE

- [1] Design Verification and Test of Digital VLSI Circuits NPTEL.

- [2] Version 2 EE IIT, Kharagpur, Module 8 Testing of embedded systems, Lesson 40 Built in Self-Test BIST for Embedded Systems, pages 3-16.

- [3] Jamuna.S,Asst Professor, Department of ECE, DSCE, International Journal of Engineering Science and Technology (IJEST) Bangalore, Implementation of BIST Structure using VHDL for VLSI circuits.