# Ultra-Low-Power and Area- Efficient Design of a Weighted Pseudorandom Test-Pattern Generator for BIST Architecture

Anam<sup>1</sup>, Dr. Manju Devi<sup>2</sup>

<sup>1</sup>M. Tech, VLSI & Embedded Systems, The Oxford College of Engineering, Bangalore- 560068. <sup>2</sup>Professor &Head, Dept. of ECE, The Oxford College of Engineering, Bangalore- 560068.

Abstract-A test pattern generator generates a pseudorandom test pattern that can be weighted to reduce the fault coverage in a built-in self-test. The objective of this paper is to propose a new weighted TPG for a scan-based BIST architecture. The motivation of this work is to generate efficient weighted patterns for enabling scan chains with reduced power consumption and area. Additionally, the pseudo-primary seed of TPG is maximized to obtain a considerable length in the weighted pseudorandom patterns. The maximum-length weighted patterns are executed by assigning separate weights to the specific scan chains using a weight-enabled clock.

Keywords: BIST, TPG, Genus

### 1. INTRODUCTION

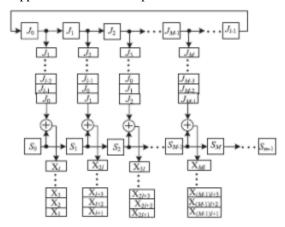

Modern technology has focused on developing lowpower systems for very-large-scale integration (VLSI) high-speed designs. As a result, several design strategies have been implemented to mitigate tradeoffs between performance, power, and area. Instead, several approaches have concentrated on low-power dissipation during BIST normal-mode operations rather than test-mode operations. During the BIST test mode operation, the switching activity in the scan chains and test data compression using the appropriate TPG are crucial. Moreover, this testing should be achieved with high reliability and sensitivity in semiconductor designs. Figure 1 illustrates an example of a conventional pseudorandom TPG. The TPG linear function is accomplished according to the output feedback signal and the input seed bits. Its linear functionalities are used in many applications such as aircraft systems, cockpit systems, medical systems, audio and video systems, and power generation and distribution systems. A TPG consists of deterministic,

exhaustive, pseudorandom, pseudorandom-weighted, and mixed-mode outputs. The pseudorandomweighted output is used to achieve higher fault coverage in many BIST structures. The weighted pseudorandom TPG exhibits true randomness and repeatable patterns in all clock cycles. Typically, it requires one seed bit to produce one test pattern for ncycles of the scanning phase in the test-per-scan BIST, where n is the scan chain length. The latest study decreased the switching activity during scan shift cycles. Additionally, the TPG allows the automatic selection of weighted parameters to achieve its low power. The weighted pseudorandom TPG methods and their implementation in can effectively reduce the switching transitions. However, the methods included additional XOR transitions between the shift registers, it consumed more power and area. The concerned drawbacks are eliminated in the proposed design effectively.

The BIST requirements should mainly focus on the higher fault coverage and the lesser weighted switching activity with lower power and reduced area overhead. To achieve these requirements, two approaches can be utilized. One is to alter the circuit design of the weighted TPG. The other is to include additional hardware in the weighted TPG. Hence, in this paper, a new pseudorandom-weighted TPG is constructed using additional hardware. Additionally, higher fault coverage is achieved in terms of eliminating transition delay faults using test-point insertion. The test-points are inserted for every two NAND gate structures of the overall design area. The proposed technique involves swapping weighted test patterns to the scan chains using a phase shifter. The swapping of the weighted patterns considered for selecting the prior scan chains with lesser area is

compared with that of the other scan chains. The weighted patterns are hence used with all the scan chains of BIST architecture. This eliminates the faults at a specified output and improves the fault coverage's. The TPG also improves its rapid switching activity due to its selected weighted patterns and reduces its average scanning and capturing power consumption during BIST test-per-scan.

### 2. EXISTING METHODOLOGIES

The test patterns for BIST can be generated by MSIC-TPG using test per clock scheme or an architecture consisting of a Gray counter, Decoder and accumulator. The test vectors generated are applied to the multiplier circuit and faults are detected by comparing the response of the circuit with the expected response.

# 2.1 Pattern Generation

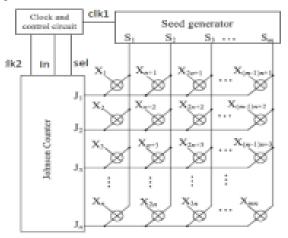

The pattern generation method for MSIC vectors uses econfigurable Johnson counter, seed vector and x-or operation. For every clock pulse, reconfigurable Johnson counter generates Johnson vector and the Linear feedback shift register generates a seed [9]. The Exclusive-or operations are done between Johnson counter and the seed vector in order to produce the test patterns. These produced vectors are shifted in to scan chains [9]. In the next clock pulse, the Johnson vectors will be circularly shifted and will bit-xor with seed. The resulted test patterns will be shifted in to the scan chains. The procedure is repeated until all the scan cells are loaded. Finally, the generated test vectors will be applied to the 4\*4 multiplier circuit.

Figure 1.1: Test pattern Generation 2.2 Reconfigurable Johnson counter

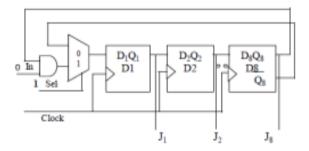

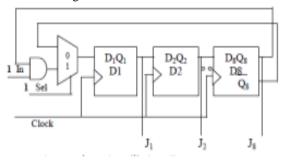

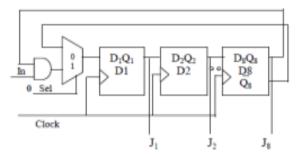

The three different modes of operation for reconfigurable Johnson counter are initialization mode, circular shift mode and normal mode. Reconfigurable Johnson counter is constructed by using AND gate, a multiplexer and eight delay flip flops.

Figure 1.2: Initialization mode

Figure 1.3: Circular shift mode

Figure 1.4: Normal mode

In initialization mode as shown in the fig 2, the reconfigurable Johnson counter will be initialized to all zero states by keeping 'sel' input of multiplexer at a value 1. In circular shift mode, the 'sel' input is made 1 and the input to the AND gate 'in' is made 1 by which the output Q8 is feedback as shown in the fig 3. To operate the reconfigurable Johnson counter in normal mode as shown in the fig 4, the 'sel' input of multiplexer is made 0 by which the inverted output of the last delay flip flop will be feedback.

# 2.3 TPG using test per clock

The outputs of the Johnson counter and seed generator are applied to the x-or gate to produce the test patterns. The clock and control circuit produces the clk1 and clk2 signals. The clk1 and clk2 are applied to the seed generator and Johnson counter respectively in order to produce the seed and Johnson vectors.

Figure 1.5: Pattern generation

The procedure for pattern generation is as follows

- 1. By applying clk1 to seed generator, the seed is produced.

- 2. A new Johnson vector is produced every time by clocking clk2.

- 3. By repeating 2, 21 Johnson vectors are generated.

- 4.For expected fault coverage, the steps 1-3 are repeated.

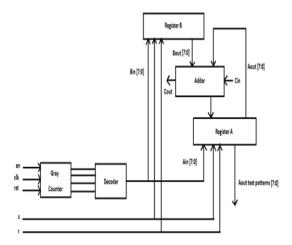

# 2.4 TPG using Gray counter

The test pattern generation using Gray counter, Decoder and accumulator architecture is shown in fig 1.6. The purpose of using gray counter is to prevent the unwanted signal transition at the input. As the patterns produced by the gray code counter has only single bit change between the subsequent test vectors, power optimization can be achieved. For every clock pulse, a 4- bit gray code is applied to the 3 to 8 decoder. The output of decoder is applied to the register B. The set and reset inputs are given to the registers in order to store the result. The outputs of two registers are given to a ripple carry adder and the final output test patterns are obtained from register A. The produced patterns are applied to the 4\*4 multiplier circuit and the response obtained is compared with the forecasted result to verify the functioning of the circuit.

Figure 1.6: TPG using Gray counter

# 3. Proposed methodology

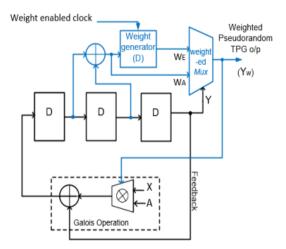

Compared with the existing methods, the proposed weighted TPG is designed with some advantages, including fewer switching transitions achieved using the specie weighted patterns and reduced power attained using fewer hardware components in the design. This reduces the hardware over-head and improves the fault coverage's in the BIST. The TPG method shown in Figure 1.7 is the proposed TPG, which includes the Galois operation and additional hardware for weighted pattern generation. The Galois operation in the proposed TPG is shown by the black dashed line and assumes constant pseudo-primary seeds (A, X) for simplification. However, the constant seed bits can be enlarged using the same subset of initial primary seeds. The seed subsets are used to achieve the maximum length in weighted patterns with less switching activity.

The additional hardware indicated by the blue line uses a smaller number of components for generating the weighted pseudorandom TPG output. In addition, the additional hardware design uses a weight- enabled clock, which enables specie weights through successive clock cycles. The particular weights are given to the respective scan chains through the weighted Mux. The weight generator clock selection effectively reduces the fault coverage in terms of the random-pattern resistant fault and the redundant faults in the BIST architecture. A 3-bit pseudorandom TPG is proposed according to the Galois scheme over a field of GF (2m). The test patterns are generated concurrently using the shift registers and Galois operation. The synchronous clock for the TPG leads

the bit sequences to be lost while it is incorporated for m-bits. Hence, the m-bit TPG is designed using asynchronous clocks in shift registers. The input vector bit (X) is multiplied continuously by the pseudo-primary seed bit (A) and added to the test vectors (Z). In addition, the state of the registers accommodates the multilevel parallelism in the TPGs. Consequently, the next (iC1)-th state after the i-th state is described in terms of the feedback loop structure.

Figure 1.7: Proposed 3-bit weighted pseudorandom TPG

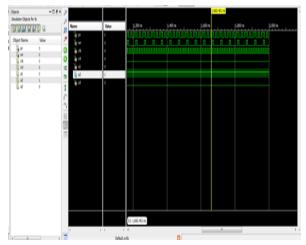

## 4. Simulation results & Comparison

The test pattern generation for BIST using different methodologies is coded in Verilog and implemented using Xilinx ISE 14.2 software. First, the weighted patterns WA generated with the probabilities of having '0' or '1' assigned to the certain scan chains occupy a smaller area. The output of the weighted Mux depends on the important feature of the pseudo randomness of the seed inputs. Consider a case in which Y0 will be swapped with Y1, Y2 until Yn, according to the value of the Galois operation (Z) in the proposed 3-bit TPG. Here, Y2 is Y, which is connected to the selection input of the Mux. This determines the weighted pattern. Hence, overall switching transitions in the scan chain primary inputs can be reduced by 25%.

Figure 1.8: Proposed 3-bit weighted pseudorandom TPG

### 4.1 Cadence RTL Genus Tool

A standard cell design methodology makes use of standard cell library of a particular process technology and synthesizes the design. Synthesizing the design involves use of standard cells, constraint file, timing files of the technology used and produces a gate-level netlist made out of logic gates such as- AND, INV, Flip-Flop, OR etc. The gate-level netlist is obtained after running the synthesis. A gate-level netlist is a description of the circuit in terms of gates and connections between them. This gate-level netlist is again simulated using simulation software's to verify the correct functionality of the design. This sub-step is called post-synthesis gate-level simulation.

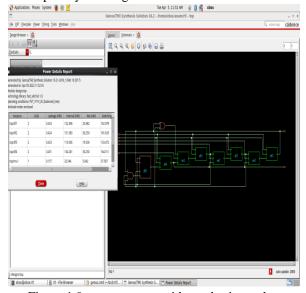

Figure 1.9: power report with synthesis results

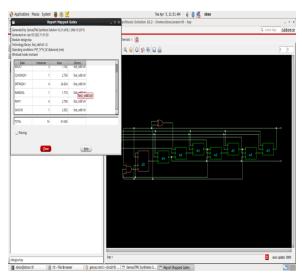

Figure 1.10: Area report with synthesis results

### **COMPARISONS**

| Related<br>work       | Circuit techniques                                                                                    |                                                                                             | Objectives for scan                                                                                    | Problem                                                                                                                                                                  | Power<br>reducti | Area-<br>efficie |

|-----------------------|-------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------|

|                       | Pseudorandom TPG                                                                                      | Weighted Pseudorandom<br>TPG                                                                |                                                                                                        |                                                                                                                                                                          | 00               |                  |

| Jinyi et al.<br>[5]   | Gators adder and Gators<br>multiplier for each tapping<br>bit used                                    | Not applicable for weighted patterns                                                        | No scan-in test done                                                                                   | Failed to produce weighted patterns                                                                                                                                      | No               | No               |

| Barry et<br>al. [17]  | Galois adder and Galois<br>multiplier for each tapping<br>bit used                                    |                                                                                             | Alternative clock<br>values of logic '0' and<br>'1' used                                               | Inefficient low-power operations for all scan chains                                                                                                                     | No               | No               |

| Xiang et<br>al. [18]  | Galois adder for each tapping bit used                                                                |                                                                                             | The test enabled                                                                                       | More propagation delay<br>and complicated design                                                                                                                         | Yes              | No               |

| Prasad et<br>al. [16] | Multiplexer for each<br>tapping bit and one XOR<br>for convolution are used                           | Additional hardware components used                                                         |                                                                                                        | Higher switching transitions                                                                                                                                             | Yes              | Yes              |

| Hwasoo<br>et al. [19] | Galois adder for each bit<br>used                                                                     | Additional hardware<br>components and XOR gates<br>successive Galois adder<br>are used      | Chains of XOR gates<br>are used with a D flip-<br>flop estimator                                       | Insufficient weighted<br>patterns for larger pseudo-<br>primary input                                                                                                    | No               | Yes              |

| Proposed              | One Galois adder, one<br>Galois multiplier used for<br>all tapping bits with an<br>asynchronous clock | Additional hardware components including weight generator and weighted multiplexer are used | Weight-enabled clock used to enable the weights W <sub>E</sub> , W <sub>A</sub> using weight generator | Eliminated the problem of<br>previous authors' work by<br>using different valued<br>weights. However, little<br>propagation delay exists in<br>the weight-enabled clock. | Yes              | Yes              |

# **CONCLUSION**

We have proposed a modified pseudo random architecture based on the development of VLSI architecture. In addition, according to the properties of pseudo random systems, based on different digital logic gates are proposed and designed. Moreover, an approximated VLSI structure computation method is

designed and proposed. The simulation results are carried out from Xilinx 14.3 and synthesis results are extracted from Cadence Genus tool using 90nm technology.

## **REFERENCES**

- [1] B. Lfsr, S. O. A. Novel, A. S. Abu-Issa, and S. F. Quigley, "Short papers," vol. 28, no. 5, pp. 755\_759, 2009.

- [2] Pomeranz, "Computing seeds for LFSR-based test generation from nontest cubes," *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.*, vol. 24, no. 6, pp. 2392\_2396, Jun. 2016, doi: 0.1109/TVLSI.2015.2496190.

- [3] Sasi, A. Amirsoleimani, A. Ahmadi, and M. Ahmadi, "Hybrid memristor-CMOS based linear feedback shift register design," in *Proc. 24th IEEE Int. Conf. Electron., Circuits Syst. (ICECS)*, Dec. 2017,pp. 62\_65, doi: 10.1109/ICECS.2017.8292094.

- [4] G. N. Balaji and S. C. Pandian, "Design of test pattern generator (TPG) by an optimized low power design for testability (DFT) for scan BIST circuits using transmission gates," *Cluster Comput.*, vol. 22, no. S6,pp. 15231\_15244, Nov. 2019, doi: 10.1007/s10586-018-2552-x.

- [5] J. Zhang, Q. Zhang, and J. Li, ``A novel TPG method for reducing BIST test-vector size," in *Proc. Int. Symp. High Density Design Packag. Microsyst. Integr.*, no. 149, Jun. 2007, pp. 6\_9, doi: 10.1109/HDP.2007.4283639.

- [6] S. Hellebrand, S. Tarnick, J. Rajski, B. Courtois, and T. I. M. Imag, "Multiple-polynomial linear feedback shift registers," 1992, pp. 120\_129.

- [7] X. Lin and J. Rajski, "Adaptive low shift power test pattern generator for logic BIST," in *Proc. Asian Test Symp.*, 2010, pp. 355\_360, doi:10.1109/ATS.2010.67.

- [8] S. Abu-Issa, "Energy-ef\_cient scheme for multiple scan-chains BIST using weight-based segmentation," *IEEE Trans. Circuits Syst. II, Exp.Briefs*, vol. 65, no. 3, pp. 361\_365, Mar. 2018, doi: 10.1109/TCSII.2016.2617160.

- [9] G. S. Sankari and M. Maheswari, "Energy ef\_cientweighted test pat- tern generator based bist architecture," in *Proc. Int. Conf. I-SMAC (IoT Soc. Mobile, Anal. Cloud), I-SMAC*, 2019, pp. 448\_453, doi: 10.1109/I-SMAC.2018.8653768.

- [10] R. Kapur, S. Patil, T. J. Snethen, and T. W. Williams, "A weighted ran- dom pattern test generation system," *IEEE Trans. Comput.-Aided Design Integr. Circuits Syst.*, vol. 15, no. 8, pp. 1020\_1025, Aug. 1996, doi: 10.1109/43.511581.

- [11] Jas, C. V. Krishna, and N. A. Touba, "Weighted pseudorandom hybrid BIST," *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.*, vol. 12, no. 12, pp. 1277\_1283, Dec. 2004, doi: 10.1109/TVLSI.2004.837985.

- [12] D. Xiang, M. Chen, and H. Fujiwara, "Using weighted scan enable signals to improve test effectiveness of scan-based BIST," *IEEE Trans. Comput.*,vol. 56, no. 12, pp. 1619\_1628, Dec. 2007.

- [13] H.-C. Tsai, K.-T. Cheng, and S. Bhawmik, "On improving test qual-ity of scan-based BIST," *IEEE Trans. Comput.-Aided Design Integr. Circuits Syst.*, vol. 19, no. 8, pp. 928\_938, Aug. 2000, doi: 10.1109/43.856978.

- [14] N. A. Touba and E. J. McCluskey, ``Altering a pseudo-random bit sequence for scan-based BIST," in *Proc. IEEE Int. Test Conf.*, Oct. 1996,pp. 167\_175, doi: 10.1109/test. 1996.55 6959.

- [15] G. Kiefer, H. Vranken, E. J. Marinissen, and H. J. Wunderlich, "Appli- cation of deterministic logic BIST on industrial circuits," *J. Elec-tron. Test. Theory Appl.*, vol. 17, nos. 3\_4, pp. 351\_362, 2001, doi:

- [16] R. Cited and A. Banerjee, U.S. Patent, 2019, vol.

- [17]B. W. Johnson, J. H. Aylor, and H. H. Hana, "Ef\_cient use of time and hardware redundancy for concurrent error detection in a 32-bit VLSI adder," *Comput. Arith.*, vol. 23, no. 1, pp. 171\_178, 2015, doi:10.1142/9789814641470.

- [18] D. Xiang, X. Wen, and L.-T. Wang, `Low-power scan-based built-in self-test based on weighted pseudorandom test pattern generation and reseeding," *IEEE Trans. Very Large Scale Integr. (VLSI) Syst.*, vol. 25, no. 3, pp. 942\_953, Mar. 2017, doi: 10.1109/TVLSI.2016.2606248.

- [19] H. Shin, S. Choi, J. Park, B. Y. Kong, and H. Yoo, "Area-ef\_cient error detection structure for linear feedback shift register," *Electronics*, vol. 9, no. 1, pp. 1\_10, 2020.

- [20] H. Dau, I. M. Duursma, H. M. Kiah, and O. Milenkovic, "Repairing Reed\_Solomon codes

- with multiple erasures," *IEEE Trans. Inf. The-ory*, vol. 64, no. 10, pp. 6567\_6582, Oct. 2018, doi: 10.1109/TIT.2018.2827942.

- [21] P. Wohl, J. A. Waicukauski, G. A. Maston, and J. E. Colburn, "XLBIST: X-tolerant logic BIST," in *Proc. IEEE Int. Test Conf. (ITC)*, Oct. 2018,pp. 1\_9, doi: 10.1109/TEST.2018.8624738.

- [22] E. Moghaddam, N. Mukherjee, J. Rajski, J. Solecki, J. Tyszer, and J. Zawada, "Logic BIST with capture-per-clock hybrid test points," *IEEE Trans. Comput.-Aided Design Integr. Circuits Syst.*, vol. 38, no. 6,pp. 1028\_1041, Jun. 2019, doi: 10.1109/TCAD.2018.2834441.

- [23] H. Tran, "Demonstration of 5TSRAMand 6T dual-portRAMcell arrays," in *IEEE Symp. VLSI Circuits*, *Dig. Tech. Paper*, Jun. 1996, pp. 68\_69, doi:10.1109/vlsic.1996.507719.

- [24] S. Roy, B. Stiene, S. K. Millican, and V. D. Agrawal, "Improved random pattern delay fault coverage using inversion test points," in *Proc. IEEE 28th North Atlantic Test Workshop (NATW)*, May 2019, pp. 1\_6, doi:10.1109/NATW.2019.8758727.

- [25] C. Senthilpari, K. Diwakar, and A. Sinh, "Low energy, low latency and high-speed array divider circuit using a Shannon theorem-based adder cell," *Recent Patents Nanotechnol.*, vol. 3, no. 1, pp. 61\_72, Jan. 2009,doi: 10.2174/18722100978 7003311.

- [26] C. Senthilpari, A. K. Singh, and K. Diwakar, "Design of a low-power, high performance, 8\_8-bit multiplier using a Shannon-based adder cell," *Microelectron. J.*, vol. 39, no. 5, pp. 812\_821, May 2008, doi:10.1016/j.mejo.2007.12.016.

- [27] R. F. W. Coates, G. J. Janacek, and K. V. Lever, "Monte Carlo simulation and random number generation," *IEEE J. Sel. Areas Commun.*, vol. SAC-6,no. 1, pp. 58\_66, Jan. 1988, doi: 10.1109/49.192730.