# Design of ANN and ANFIS Controller Based UPFC Embedded with Three Level Cascaded H Bridge Inverter with SPWM Technique for Fast Restoration of Power Following Severe Transient Conditions on Transmission Lines

T.JaganMohanRaju 1, Prof. G.Tulasi Ram Das <sup>2</sup>

<sup>1</sup>Assistant Professor of EEE, Kakatiya University, JNTUH Hyderabad

<sup>2</sup>Professor of EEE, Kakatiya University, JNTUH Hyderabad

Abstract: Performance improvement of UPFC with reference to the transient stability and Dynamic stability enhancement incorporating Fuzzy Logic controller in place of proportional integral controller is analysed. The UPFC is embedded with a 3 level cascaded H Bridge inverter. The Response time taken by UPFC with fuzzy controller is very less. Cascaded H Bridge Inverters offer high level of Voltage Support, Low Switching Stress and Good Modularity. The system response to the Reference commands or the correction commands is very faster when compared to PI controller based UPFC. This aspect is shown by calculating the times like settling time in all the four cases of faults like LG, LL, LLG, LLL and also even when the loads are changed from normal to highly Inductive and highly capacity the UPFC help the Power System Network to Restore normalcy in a less time. UPSC is connected to the IEEE 5 bus system between the buses 3 and 4 for checking its capabilities. The improvement in the performance of UPFC with fuzzy based controller over conventional PI controller is depicted in the end result. Simulations results prove that a FUZZY LOGIC Controller Based UPFC has a better performance rate then a PI Controller based UPFC. The Simulations are carried using MATLAB Software.

Keywords – AC Transmission, FACTS, UPFC, IEEE-5 BUS System, Shunt Line Faults, Power Flow Control, Cascaded H Bridge (CHB) Inverters, SPWM, PI Controller, FUZZY LOGIC Controllers, Rise Time, Settling Time.

# 1. INTRODUCTION

The Unified Power Flow Controllers were basically proposed for real time control and dynamic compensation of the ac transmission system parameters and for obtaining more flexibility in solving the problems faced by the utilities. An earnest effort towards achieving the above goals is made here especially to improve the sensitivity of the device, the quality of output of the device, the response time of the device and also the controllability of the device by making the device to act like a self thinking machine. The Unified Power

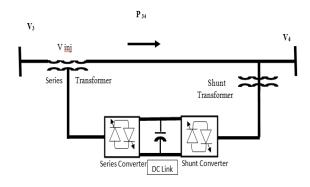

Flow Controller has two converters, one a shunt converter (converter 1), connected in shunt with the transmission network and other a series converter (converter 2), connected in series with the Transmission Network These two converters are connected to each other by a common DC link capacitor. The presence of a common DC link enables the transfer of real and reactive power to flow between the two converters thereby enabling the absorption and injection of voltages and currents from and to the transmission network respectively. Each of the converters can independently generate and absorb real and reactive power at their respective ac terminals. The basic function of the Shunt converter (converter 1) is to supply the real power it can also supply or absorb reactive power. The series converter (Converter 2) provides the main function of the UPFC by injecting an ac voltage of requisite magnitude Vpq  $(0 \le Vpq \le Vpqmax)$  and phase angle  $\delta (0 \le \delta \le \delta max)$ at power frequency in series with the transmission line voltage.

# UPFC FUNDAMENTAL CONFIGURATION

Terminal Voltage Regulation is done with UPFCs wherein the required voltage of change required on the Transmission line say,  $\Delta V$  (Vinj), is injected either in-phase or in anti-phase mode with the existing voltage Vo on the Transmission line.

Series Capacitive Compensation is done where the required value of voltage say, Vinj, is injected in Quadrature with the Line Current.

Phase Shifting or Transmission Angle Regulation is done by injecting a voltage of Vinj in an angular relationship with Vo to get the required Phase Shift (Advanced or Retarded) in the Line output voltage without change in the Magnitude of the Line output voltage.

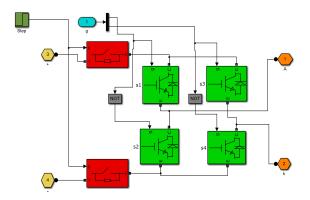

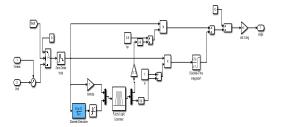

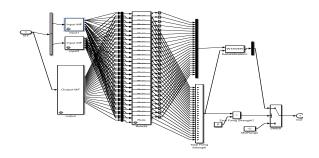

Fig.3. Three Level CHB Based UPFC for IEEE-5 Bus System Using FUZZY LOGIC Controller

In the explanation that follows, the importance of using the FUZZY LOGIC Controllers in UPFC to enhance the Controlling Capabilities of UPFC are clearly explained. The UPFC incorporating a 3 Level CHB Inverter and a Fuzzy Logic Controller is tested for its improved performance on a Standard IEEE -5 Bus System. The UPFC is connected in the system between Bus number 3 and 4. The test conditions include (i) under voltage compensation (due to Increase in Inductive Load), (ii) over voltage compensation (due to Light load conditions or due to Capacitive over Loadings), (iii) Transient Stability Enhancement Capabilities when the IEEE-5 Bus system is subjected to different Shunt Faults like LG,LL,LLG and LLL Faults at Bus No. 4. The PI controllers are best known to be the fundamental Controllers in restoring Normalcy on a Power System Network. The immediate changes in the network conditions, more importantly, at the point of connection of the UPFC are detected and Appropriate Corrective Actions are initiated by the FUZZY LOGIC Controllers. The UPFC Simulated in this paper mainly consists of a Three level Cascaded H Bridge Inverter. The Sinusoidal Pulse Width Modulation Technique (SPWM) is used .The Advantage with the CHB Inverters is made use of in improvising the Performance of the UPFC there by Improving the Protection Levels offered to the Power System Network when the Power System is subjected to Certain Adverse and Abnormal Conditions. One of the most widely used software MATLAB is used for simulating the said test conditions.

# The Cascaded H Bridge Inverter

One of the outcomes of the Research on the attempt to improvising the Output Voltage of an

Inverter through Modifying Network/Circuit configurations of an Inverter is the Cascaded H Bridge (CHB) Inverter. The low switching voltage stress and modularity has made the Multi Level Inverters (MLIs) gain more attention. The user desired Multi Level voltage is obtained by using different and separate voltage sources like Batteries, Fuel cells, Solar Photo Voltaic (PV) Cells, Capacitors etc., The major Advantages with Multi Level Inverters are their Minimum Harmonic Distortions in the Output Voltage, Low Electro Magnetic Emissions, High output to Input Ratios i.e., High Efficiency and More Importantly their High Voltage With Standing and Operating Capability and Modularity. The Multi Level Inverters have found great applications in the areas of Drive Controls, Uninterruptible Power Suppliers and Static Volt Ampere Reactive Generators (SVG).In general MLIs are divided in to three categories as Diode Clamped, Flying Capacitor and Cascaded Bridge Inverters. One of the advantages of MLIs over the Two Level Inverter is that they reduce the Common Mode Voltage causing the breaking leakage Current in Multi Drive Systems of High Power Ratings (Greater Than 250KW) based Vehicles.

The Circuit Topology of Cascaded H Bridge Inverter

Fig.4.Basic Circuit of a CHB Inverter used in this Simulation

Fig.5.The 3 Level Cascaded H Bridge Inverter used in this Simulation

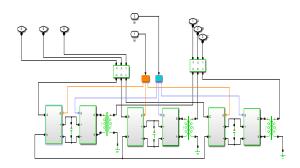

# THE CENTRAL CONTROL SYSTEM

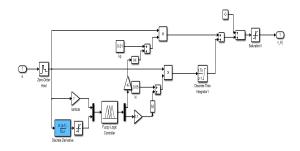

Fig.6. The Central Control System Comprising of the Series and Shunt Controllers including the SPWM Based Pulse Generator

Fig.7. The AFIS Based Shunt Controller

Fig.8. The ANFIS Based Series Voltage Injection Controller

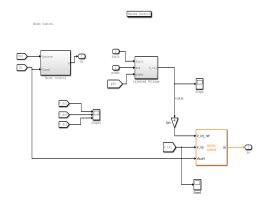

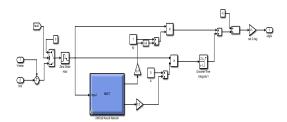

# THE ANN CONTROLLER

Fig.9(a) ANN CONTROLLER

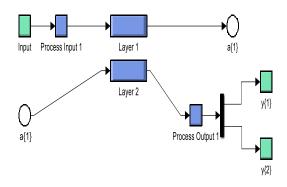

Fig.9(b).The Internal Structure of the ANN controller

# © August 2022 | IJIRT | Volume 9 Issue 3 | ISSN: 2349-6002

Fig.10. The Internal Structure of an ANFIS Controller

# **OUTPUTS**

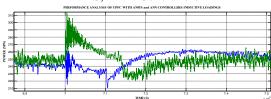

Fig.11(a). The Complete Power Transferred Through the Line 3-4 under different Test Conditions Using ANFIS AND ANN Controller

Fig.11(b). The Initial Power Swing Through the Line 3-4 under different Test Conditions Using ANN and ANFIS Controllers

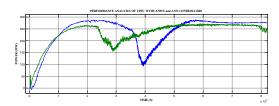

Fig.12. Power Transferred Through the Line During LG Fault with a ANN and ANFIS Controllers

Fig.13. Power Transferred Through the Line During LL Fault with ANN and ANFIS Controller

Fig.14. Power Transferred Through the Line During LLG Fault with a ANN and ANFIS Controllers

Fig.15. Power Transferred Through the Line During LLL Fault with an ANN and ANFIS Controller

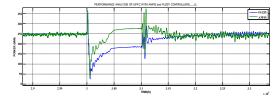

Fig.16. Power Transferred Through the Line During INDUCTIVE LOADING, with an ANFIS, ANN Controllers

Fig.17. Power Transferred Through the Line During CAPACITIVE OVER LOADING with an ANFIS and ANN Controller

TABLE 1 RESULTS TABULATION

| S.No | TYPE OF<br>DISTURBA<br>NCE                                     | DURATI<br>ON OF<br>DISTUR<br>BANCE<br>IN<br>SECOND<br>S | SETTLING TIME IN<br>SECONDS<br>(EXACT TIME) |                         |

|------|----------------------------------------------------------------|---------------------------------------------------------|---------------------------------------------|-------------------------|

|      |                                                                |                                                         | ANN<br>CONTR<br>OLLER                       | ANFIS<br>CONTR<br>OLLER |

| 1    | VOLTAGE<br>SAG                                                 | 0.5<br>(30 to<br>30.5)                                  | 34.4                                        | 32.2                    |

| 2    | VOLTAGE<br>SWELL                                               | 0.5<br>(35 to<br>35.5)                                  | 38.1                                        | 36.5                    |

| 3    | SWITCHIN G ACTION STEP CHANGE FROM INDUCTA NCE TO CAPACITA NCE | Instant<br>(at 40 th<br>Sec)                            | 43                                          | 42                      |

| 4    | LINE TO<br>GROUNG<br>FAULT                                     | 0.5<br>(10 to<br>10.5)                                  | 15                                          | 11.9                    |

| 5    | LINE TO<br>LINE<br>FAULT                                       | 0.5<br>(15 to<br>15.5)                                  | 18.6                                        | 17.4                    |

| 6    | LINE TO<br>LINE TO<br>GROUND                                   | 0.5<br>(20 to<br>20.5)                                  | 23.6                                        | 23.0                    |

| 7    | THREE<br>PHASE<br>FAULT                                        | 0.5<br>(25 to<br>25.5)                                  | 28.6                                        | 27.9                    |

The above Table 1 indicates that the UPFC embedded with a Fuzzy Logic controller has a faster response than the UPFC with a PI Controller. This Phenomenon can be observed from the fact that the Settling Time for Restoration of Normalcy during the occurrence of Different Kinds of Disturbances, like Voltage Sag, Voltage Swell or Faults like LG, LL, LLG, and LLL, is Lesser than the settling time taken by a UPFC with a PI Controller.

### REFERENCES

- [1]. Gyugyi.L "A Unified Power Flow Control Concept for Flexible AC Transmission System" IEE PROCEEDINGS –C Vol. 139 No 4, July 1992.

- [2]. Gyugyi.L "Dynamic Compensation of AC Transmission lines by Solid State Synchronous voltage Sources" IEEE/PES Summer Power Meeting

- ,Paper No.93 Sm 434-1,PWRD, Vancouver , B.C., Canada , July 1993.

- [3]. Schauder C.D. and Mehta H ,"Vector analysis and Control of advanced Static Var Compensators", IEE PROCEEDINGS-C Vol. 140 No.4 July 1993.

- [4]. A.S.Mehraban et al., "Application of World's First UPFC on the AEP System", EPRI Conference, The Future of Power Delivery Washinton D.C April 9-11,1996.

- [5]. B.A Renz, et al., "AEP Unified Power Flow Controller Performance", IEEE Transactions on Power Delivery Vol 14 No.4 Oct 1999.

- [6]. P. S Sen Sarma, K.R.Padiyar ,V Ramanayanan, "Analysis and Performance Evaluation of a DSTATCOM for Compensating Voltage Fluctuations", PE065PRD(10-2000)

- [7]. Jingsheng Liao, Kai-tak van , "Cascaded H Bridge MultiLevel Inverters a Reexamination", IEEE Proceedings on Vehicle Power and Propulsion Conference, IEEE Conference ,Sept. 2007.

- [8]. Timothy.J.E.MILLER, "Reactive Power Control in Electric Systems", John Wiley India Edition

- [9]. W.D. Stevenson "Elements of Power System Analysis" Mc Graw Hill 4<sup>th</sup> edition

- [10]. K.R Padiyar and Awanish Jaiswal "Discrete Control of SSSC for Transient Stability Improvement of Power System", national Power System Conference NPSC 2002.

- [11]. K.R.Padiyar "FACTS Controllers in Power Transmission and Distribution" New Age Publications [12]. Narain G Hingorani and Lazlo Gyugyi, "Understanding FACTS Concepts and technology of Flexible AC Transmission Systems" IEEE Press wiley India Edition.

- [13]. Padiyar "Power System Dynamics and Stability " 2dn edn.BS Publications.

- [14]. Kundur, "Power System Dynamics and Stability". EPRI, TataMc Graw Hill

- [15]. Bambang Sujanarko, "Simulation Development of Carrier Based PWM for Cascaded Multi Level Inverters" International Journal of Computer Applications (0975-8887) Vol 104- No.5 October 2014

- [16]. A. Ajami and H.S. Hosseini, "Application of a Fuzzy Controller for Transient Stability

Enhancement of AC Transmission System by STATCOM," *International Joint Conference SICE-ICASE*, pp. 6059-6063, 2006

[17] H.R. Van Lauta Nemke and Wang De-zhao, "Fuzzy PID Supervisor," 24th IEEE Conf. on Decision and Control, Vol. 24, pp 602-608, 1985

[18] K. M. Passino and S. Yurkovich; "Fuzzy Control" Addison-Wesley,, 199

[19]N.F Milah , S.M.Bashi , N.Marium and I Aris Dept. Of Electrical and Electronics Engineering, Faculty of Engineering, University Putra Malaysia, 43400 , Malaysia "Simulation of Three Phase Multilevel UPFC Journal of Applied Science 8(3) 503-509 , ISSN 1812-5654

[20] M.Shoba, Sree Ram kumar, Saly George "ANFIS based UPFC suppementary controller for damping low frequency oscillations in power system ", jes 2007, https:journal.esrgroups.org/jes.

# **APPENDIX**

IEEE-5 Bus System

NUMBER OF LINES = 7

NUMBER OF BUSES = 5

In all these BUS DATA's type-3 indicates slack bus, type-2 indicates PQ / load bus, type-1 indicates PV / generator bus.

# LINE DATA

| SB | EB | R (p.u) | X (p.u) | Ys    | Tap |

|----|----|---------|---------|-------|-----|

| 1  | 2  | 0.02    | 0.06    | 0.03  | 1   |

| 1  | 3  | 0.08    | 0.24    | 0.025 | 1   |

| 2  | 3  | 0.06    | 0.18    | 0.02  | 1   |

| 2  | 4  | 0.06    | 0.18    | 0.02  | 1   |

| 2  | 5  | 0.04    | 0.12    | 0.015 | 1   |

| 3  | 4  | 0.01    | 0.03    | 0.01  | 1   |

| 4  | 5  | 0.08    | 0.24    | 0.025 | 1   |

# **AUTHORS**

[1] T.JAGANMOHAN RAJU is with the Dept. of Electrical and Electronics Engineering, University College of Engineering, Kakatiya University, Kothagudem, Telangana. India.He pursued his B.Tech from DPEC, Bhadrachalam, and M.Tech fron JNTUK Kakinada.He is presently pursuing PhD from the Dept. of EEE, JNTUH Hyderabad on Part Time basis. His Research interests include Power System

- Analysis, FACTS, AI Technique Applications to Power Systems, Renewable Energy Systems.

- [2] Prof.G.TULASI RAM DAS is Presently with the Dept. of Electrical and Electronics Engineering, JNTUH Hyderabad, Telangana, India. Prof. Das obtained his B.Tech (EEE) from JNTU Hyderabad, M.Tech (Industrial Drives and Controls) from Osmania University, and PhD from IIT Madras. His Research Interests include, Power Electronics, Power Semi-Conductor Controlled Electric Drives (IM, PMSM, BLDCM, & SRM), Resonant Converters, Multilevel Converters, Flexible AC Transmission Systems (FACTS), Power Quality, Wind Energy Conversion, and Solar PV Cell Technologies