## Low Power Flip Flop Using Cadence

Akshata M Hosamani<sup>1</sup>, Suraj Kadli<sup>2</sup>

<sup>1,2</sup> Kls Vishwanath Rao Deshpande Institute of Technology, Haliyal

This the design paper investigates implementation of low-power flip-flops, specifically D, JK, and SR flip- flops, using NAND and NOR gates. In the modern era of integrated circuits, minimizing power consumption is crucial for achieving energy-efficient systems. We propose the design of basic gates (AND, OR, NAND, NOR, Inverter) using low-power techniques and implement these gates to design the flip-flops. The paper also focuses on the analysis of the power consumption and delay parameters for each flip-flop design. Power and delay metrics are calculated using simulations to compare the performance of conventional and low-power flip-flop designs. Our study shows that optimized gate designs result in reduced power dissipation and improved delay, making these flipflops suitable for low-power applications.

## Chapter 1 Introduction 1.1 Introduction

The demand for low-power circuits has risen modern electronic significantly devices. particularly in portable devices and systems- on-chip (SoCs). Flipflops are fundamental building blocks of sequential logic circuits and are used in a variety of applications, such as memory storage, counters, and registers. This paper focuses on designing D, JK, and SR flip-flops with low power consumption by optimizing the underlying logic gates- NAND and NOR gates. We also compare their power and delay performance with conventional flip-flop designs. Traditionally, flip-flops are designed using basic logic gates such as AND, OR, NAND, NOR, and NOT gates. However, these circuits tend to consume considerable amounts of power, especially in highspeed applications. Recent advancements low-power design

techniques aim to minimize power dissipation by optimizing logic gate implementations. This paper explores the benefits of using NAND and NOR gates

to design low-power flipflops.

#### 1.2 Related Work

Several techniques have been proposed to reduce the power consumption of flip-flops, including conditional data mapping, clock gating, and sleep transistors. Prior research has focused on reducing redundant transitions and optimizing transistor sizing to minimize power dissipation. Our work builds on these techniques and implements an optimized flip-flop design using the Cadence toolchain.

## Chapter 2 Literature Review

I. Low Power D Flip Flop Design for VLSI Applications

Author: A.Manikandan Year of Publication: 2021 Abstract

Power consumption is a critical concern in modern VLSI design, particularly in sequential circuits such as D flip-flops. This paper presents the design and simulation of a low-power D flip-flop using Cadence Virtuoso and Spectre simulator. Various design techniques, including clock gating, transistor sizing optimization, and conditional data mapping, are explored to achieve power efficiency. The proposed design demonstrates a significant reduction in power consumption compared to conventional D flipflops, making it suitable for low- power applications in VLSI circuits.

#### INTRODUCTION

With the increasing demand for low-power VLSI systems, optimizing the power consumption of sequential elements such as D flip-flops has become essential. Flip-flops contribute significantly to dynamic power dissipation due to frequent state transitions and clock activities. This paper explores power-efficient D flip- flop designs implemented using Cadence Virtuoso and simulated using the

## © February 2025 | IJIRT | Volume 11 Issue 9 | ISSN: 2349-6002

Spectre tool.

II. Low Power Design of Sr Flip Flop Using45nm Technology

Author: Pratiksha Gupta, Dr. Rajesh Mehra Year of

Publication: 2016

#### Abstract

Power consumption is a significant concern in VLSI design, especially for sequential circuits like SR flip-flops. This paper presents the design and simulation of a low-power SR flip-flop using 45nm CMOS technology in Cadence Virtuoso and Spectre simulator. The proposed design incorporates power optimization techniques such as clock gating, transistor sizing, and leakage reduction strategies. Simulation results indicate that the proposed SR flip-flop achieves substantial power savings while maintaining performance and reliability, making it suitable for low-power applications in modern VLSI systems.

#### Introduction

As semiconductor technology scales down, power efficiency has become a critical factor in VLSI circuits. Sequential circuits, particularly flip-flops, consume a significant portion of

dynamic and leakage power in integrated circuits. The SR flipflop is widely used in memory elements and sequential logic circuits, making its power optimization essential for energy-efficient design. This paper presents a low-power SR flip-flop designed using 45nm CMOS technology and optimized in Cadence Virtuoso.

III. Design And Simulation of Low Power JK Flip-Flop At 45nm Technology

Author: Anshu Mittal, Jagpal Singh Ubhi

Year of Publication: 2016

#### Abstract

Power consumption is a significant concern in VLSI design, especially for sequential circuits like JK flip-flops. This paper presents the design and simulation of a lowpower JK flip-flop using 45nm CMOS technology in Cadence Virtuoso and Spectre simulator. The proposed design incorporates power optimization techniques such as clock gating, transistor sizing, and leakage reduction strategies.

Simulation results indicate that the proposed JK flipflop achieves substantial power savings while maintaining performance and reliability, making it suitable for low-power applications in modern VLSI systems.

#### Introduction

As semiconductor technology scales down, power efficiency has become a critical factor in VLSI circuits. Sequential circuits, particularly flip- flops, consume a significant portion of dynamic and leakage power in integrated circuits. The JK flip-flop is widely used

in counters, shift registers, and sequential logic and circuits, making its power optimization essential for energy efficient design. This paper presents a low power JK flip-flop designed using 45nm technology.

#### Chapter 3 Methodology

The design and implementation of a low-power flipflop at 45nm technology follow a structured methodology using Cadence Virtuoso for schematic design, Spectre for simulation, and standard CMOS design principles. The methodology consists of several key stages:

## A. Design Flow in Cadence

- Schematic Design: A low-power flip- flop is designed using CMOS technology in Cadence Virtuoso, ensuring optimal transistor sizing and reduced switching activity.

- Simulation Setup: The Spectre simulator is used to analyze power consumption, propagation delay, and setup/hold times under varying conditions.

- Layout Design: The layout of the flip- flop is created in the Virtuoso Layout Editor following 45nm process design rules. Design Rule Check (DRC) and Layout Versus Schematic (LVS) verification ensure correctness.

- 4. Post-Layout Simulation: The extracted layout is simulated to evaluate real-world performance, considering parasitic effects and power consumption metrics.

- B. Power Optimization Techniques

- 1. Clock Gating: Reduces dynamic power consumption by disabling the clock signal when no state transition occurs.

- 2. Transistor Sizing: Optimizes transistor

## © February 2025 | IJIRT | Volume 11 Issue 9 | ISSN: 2349-6002

dimensions to balance speed and power consumption.

- 3. Leakage Reduction Techniques: Implements low-leakage transistors and power-gating strategies to minimize static power dissipation.

- 4. Supply Voltage Scaling: Evaluates the impact of reduced supply voltages on power and performance trade-offs.

5.

# Chapter 4 Architecture, Functionality and Logic Gates

The architecture of a low-power flip-flop is designed to reduce power consumption while maintaining performance. It typically consists of:

- 1. Master-Slave Latches: Built using transmission gates or pass transistors.

- 2. Conditional Clocking: Reducing unnecessary switching activity.

- 3. Dual-Edge Triggering: Enhancing power efficiency by reducing clock frequency.

- 4. Embedded Clock Gating: Avoiding unnecessary toggling of internal nodes.

## Chapter 5 Results and Analysis

## 5.1 D Flip flop

A D flip-flop (Data or Delay flip-flop) is a sequential logic circuit used in synchronous digital systems. It captures the input data (D) at a clock edge and stores it until the next clock cycle.

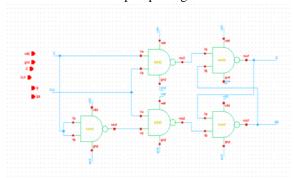

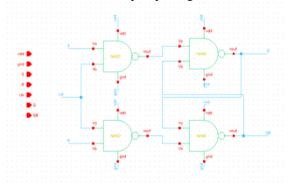

### 5.1.1 Schematic D Flip flop using NAND

Schematic diagram of D Flip flop using NAND

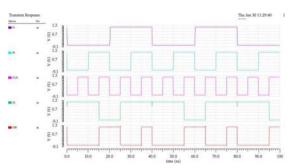

#### 5.1.2 Waveform of D Flip flop using NAND

Waveform of D Flip flop using NAND

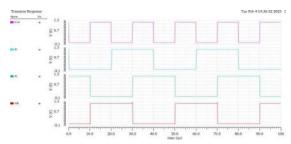

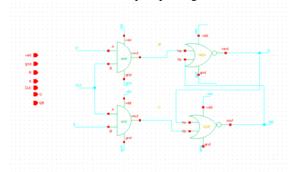

### 5.1.3 Schematic D Flip flop using NOR

schematic diagram of D Flip flop using NOR

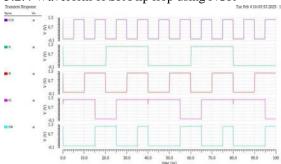

## 5.1.4 Waveform of D Flip flop using NOR

Waveform of D Flip flop using NOR

#### 5.2 SR Flip flop

An SR (Set-Reset) Flip-Flop is a bistable sequential circuit that has two inputs, S (Set) and R (Reset), and two outputs, Q and Q'. It is the fundamental building block of memory elements and latches in digital electronics.

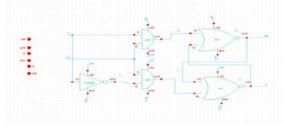

#### 5.2.1 Schematic SR Flip flop using NAND

schematic diagram of SR Flip flop using NAND 5.2.2 Waveform of SR Flip flop using NAND

## © February 2025 | IJIRT | Volume 11 Issue 9 | ISSN: 2349-6002

Waveform of SR Flip flop using NAND 5.2.3 Schematic SR Flip flop using NOR

Schematic diagram of SR Flip flop using NOR 5.2.4 Waveform of SR Flip flop using NOR

Waveform of SR Flip flop using NOR

## 5.3 JK Flip flop

The JK Flip-Flop is an improved version of the SR Flip-Flop that eliminates the invalid state (S = 1, R =1) by introducing a feedback mechanism. It is widely used in counters, shift registers, and memory circuits.

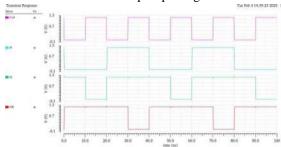

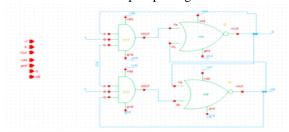

## 5.3.1 Schematic JK Flip flop using NAND

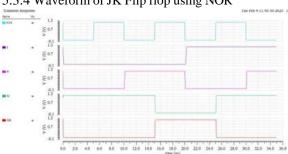

Schematic diagram of JK Flip flop using NAND 5.3.2 Waveform of JK Flip flop using NAND

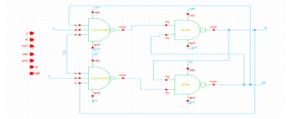

Waveform of JK Flip flop using NAND 5.3.3 Schematic JK Flip flop using NOR

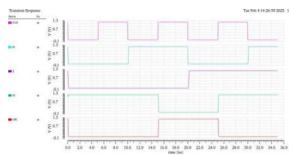

5.3.4 Waveform of JK Flip flop using NOR

Waveform of JK Flip flop using NOR

#### **RESULTS AND ANALYSIS**

| Paramet | D    |       | SR   |      | JK   |      |

|---------|------|-------|------|------|------|------|

| er      |      |       |      |      |      |      |

|         | Usin | Usin  | Usin | Usin | Usin | Usin |

| Power   | g    | g nor | g    | g    | g    | g    |

|         | nan  |       | nand | nor  | nan  | nor  |

|         | d    |       |      |      | d    |      |

|         |      |       |      |      |      |      |

|         | 370. | 525.  | 444. | 607. | 507. | 719. |

|         | 8nm  | 4nm   | 4nm  | 4nm  | 1nm  | 03n  |

|         |      |       |      |      |      | m    |

|         |      |       |      |      |      |      |

| Delay   | 20.5 | 15.0  | 17.3 | 17.6 | 23.6 | 17.0 |

|         | nsec | 5nse  | 5nse | 2nse | nsec | 5nse |

|         |      | c     | С    | С    |      | c    |

### Chapter 6 Conclusion

This study presents the design and analysis of lowpower flip-flop circuits using D, JK, and SR configurations, implemented with NAND and NOR logic gates. The schematic diagrams and waveform analysis of the designed circuits reveal that the D flip-flop circuit exhibits the lowest power consumption delay and among the configurations. The JK flip-flop circuit shows a moderate power consumption and delay, while the SR flip-flop circuit exhibits the highest power consumption and delay. Furthermore, the use of NAND gates results in lower power consumption and delay compared to NOR gates. The power consumption and delay of the flip-flop circuits are highly dependent on the clock frequency and transistor sizing. In conclusion, this study demonstrates that the D flip-flop circuit with NAND gates offers the best trade-off between power consumption and delay, making it a suitable choice for designing low-power digital systems, particularly in applications where energy efficiency is a critical concern.

#### REFERENCE

- [1] NatarajanV, Nagarajan AK, Pandian N,Savithri VG. Low Power Design Methodology. Very-Large- Scale Integration. 2018 Feb.

- [2] DurgeshNandan."Routing Strategy: Networkon- Chip Architectures."In VLSI Architecture for Signal,Speech,and Image Processing, pp.167-197.Apple Academic Press,2022.

- [3] Anjana S, Rajesh Mahra "Design and Implementation of SR flip flop for efficient Power using 90nm CMOS Technology "International Journal of Scientific Research Engineering & Technology (IJERST), Volume-2, May-2015.

- [4] Pinki & Rajesh Mehra, "Design of Low Power High Performance JK Flip Flop"International Journal of Scientific Research Engineering & Technology (IJSRE), 14-15, March 2015.