# Power Efficient Synchronous Counter Design

<sup>1</sup>Dr.L.Lakshmi Prasanna Kumar, <sup>2</sup>P.Raghu Ram Naidu, <sup>3</sup>G.Vishnu Vardhan, <sup>4</sup>B.C.Bhuvaneshwar G. Pulla Reddy Engineering College

Abstract- The performance of VLSI circuits hinges on their design architecture, focusing on optimizing power usage and enhancing reliability. Achieving low power consumption necessitates power optimization across various circuit levels. Many system-level architectures incorporate sequential circuits, whose design significantly influences the overall system power. fundamental components applications like timers, memories, and ADCs/DACs, often introduce power inefficiencies due to high clock signal power requirements and unintended flip-flop activities. This brief introduces a power-efficient design for synchronous counters, minimizing clock-related power consumption and improving reliability. Evaluated using standard 180 nm CMOS technology in CADENCE, our design outperforms current counter architectures in both power demand and power-area product, especially benefiting wide-bit counters.

Keywords-VLSI design, synchronous counters, clock gating, power efficiency, CMOS technology, CADENCE.

#### 1. INTRODUCTION

Sequential circuits play a vital role in VLSI design, particularly in computer processes synchronized with clock cycles. Power management is crucial for portable and mobile devices, influenced by high frequencies and chip sizes. Power dissipation in circuits primarily consists of static and dynamic components, with dynamic power being dominant due to signal transitions and short-circuit currents. Counters, essential in VLSI systems, contribute significantly to power consumption due to high clock unintended flip-flop Synchronous counters, driven by simultaneous clock pulses, offer speed and reliability advantages over asynchronous counters. However, existing architectures face limitations such as propagation delays, hardware complexity, and power overhead. This work proposes a novel clock gating technique to reduce power consumption while maintaining minimal hardware overhead.

#### 2. LITERATURE REVIEW

Traditional synchronous counters use edge-triggered D-type or JK-type flip-flops with a shared clock signal. Logic gates (AND, OR, NOT) control flip-flop toggling to achieve counting sequences. For example, a 4-bit up-counter requires sequential state transitions from 0 to 15.

#### Drawbacks:

- Increased Power: High clock load and unnecessary flip-flop activities.

- Complexity: Additional circuitry for state transitions.

- Latency: Propagation delays in logic gates.

Prior works explored adiabatic logic, priority encoding, and quasi-synchronous designs but faced trade-offs in complexity and efficiency.

# 3. PROPOSED METHODOLOGY

A power-efficient synchronous counter is proposed using:

- T Flip-Flops: Detect state changes, reducing power during inactivity.

- Combinational Clock Gating: An AND gate and control transistor selectively activate the master clock based on preceding flip-flop states.

- Truth Table Optimization: Equations derived for a 4-bit counter ensure efficient clock signal management.

# **Key Innovations:**

- Reduced active clock load by 50% compared to traditional designs.

- Scalable architecture for wider-bit counters (e.g., 8-bit, 16-bit).

- Minimal hardware overhead (one AND gate and transistor per stage).

Simulation Setup:

Tools: CADENCE Virtuoso (180 nm CMOS technology).

# © April 2025 | IJIRT | Volume 11 Issue 11 | ISSN: 2349-6002

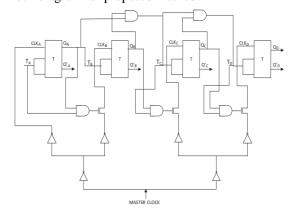

Metrics: Power consumption, area, and delay. Block diagram for proposed method:

Existing method results for power:

Existing Method Results for Delay:

Existing Method Results for the no of Transistors

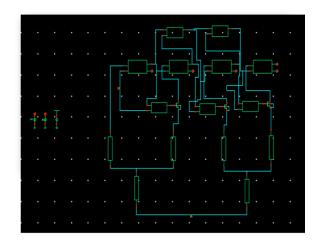

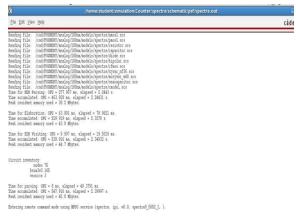

Circuit inventory:

nodes 69

bsim3v3 153

vsource 3

# 4. RESULTS

Schematic:

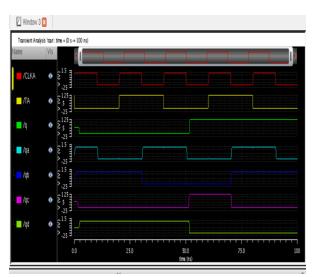

Waveforms:

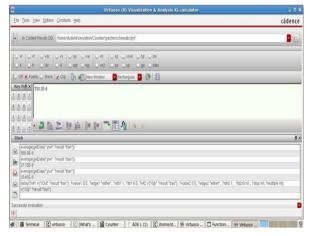

Power:

# Delay:

# No of Transistors:

# 5. Applications

- Embedded Systems: Low-power timers and schedulers.

- Automotive Electronics: Energy-efficient sensor interfaces.

- Industrial Automation: High-reliability control units.

- SAR ADC Integration: Demonstrated 25% power savings in digital blocks.

#### 6. CONCLUSION

The proposed synchronous counter design leverages clock gating and T flip-flops to minimize power consumption and hardware complexity. Simulations confirm significant improvements in power-area efficiency, particularly for wide-bit counters. Future work includes optimizing transistor sizing and extending the design to asynchronous-reset applications.

### **REFERENCE**

[1] S. Bhowmik, D. Deb, S.N. Pradhan, B.K. Bhattacharyya, Reduction of noise using continuously changing variable clock and clock

- gating for IC chips, *IEEE Trans Compon Packag Manuf Technol* 6 (6) (2016) 886–896.

- [2] C.S. Ragit, S. Badjate, Design of up-down counter as SAR logic for high speed SAR ADC used in health care system, 2016 Conference on advances in signal processing (CASP), Pune, 2016, pp. 465–468.

- [3] S.M. Ismail, A.B.M.S. Rahman, F.T. Islam, Low power design of johnson counter using clock gating, 2012 15th International conference on computer and information technology (ICCIT), Chittagong, 2012, pp. 510–517

- [4] Q. Wu, M. Pedram, X. Wu, Clock-gating and its application to low power design of sequential circuits, *IEEE Trans Circuits Syst I* 47 (3) (2000) 415–420.

- [5] J.M. Rabaey, A. Chandrakasan, B. Nikolic, Digital integrated circuits: A design perspective, Prentice Hall, 2003.

# Digital Library

- [1] N.H.E. Weste, D. Harris, A. Banerjee, CMOS VLSI design, 3rd edition, Dorling Kindersley Pvt. Ltd., 2006.

- [2] S.H. Unger, Double-edge-triggered flip-flops, IEEE Trans Comput 30 (6) (1981) 447–451.

- [3] X. Wu, M. Pedram, Low power sequential circuit design using priority encoding and clock gating, power electronics and design, 2000. ISLPED '00, Proceedings of the 2000 international symposium on, 2000, pp. 143–148.

- [4] T. engineering (ICMETE), Ghaziabad, 2016, pp. 584–586.

- [5] X. Wu, J. Wei, M. Pedram, Low-power design of sequential circuits using a quasi-synchronous derived clock, Proceedings 2000. design automation conference. (IEEE Cat. No.00CH 37106), Yokohama, Japan, 2000, pp. 345–350.

- [6] Y.T. Hwang, J.F. Lin, Low voltage and low power divide-by-2/3 counter design using pass transistor logic circuit technique, IEEE Trans Very Large Scale Integr VLSI Syst 20 (9) (2012) 1738–1742.

- [7] Doi, V. Niranjan, Low power and high performance ring counter using pulsed latch technique, 2016 International conference on micro-electronics and telecommunication